Анонс Altera Stratix 10

Получил письмо Newsroom Notification из Альтеры. Периодически они присылают разные анонсы, ну и читаю их постоянно.

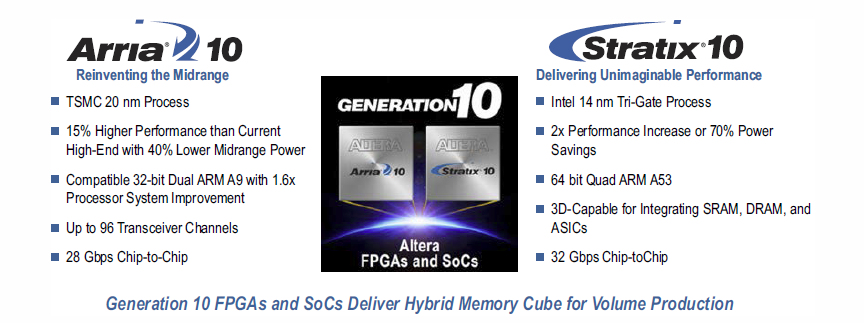

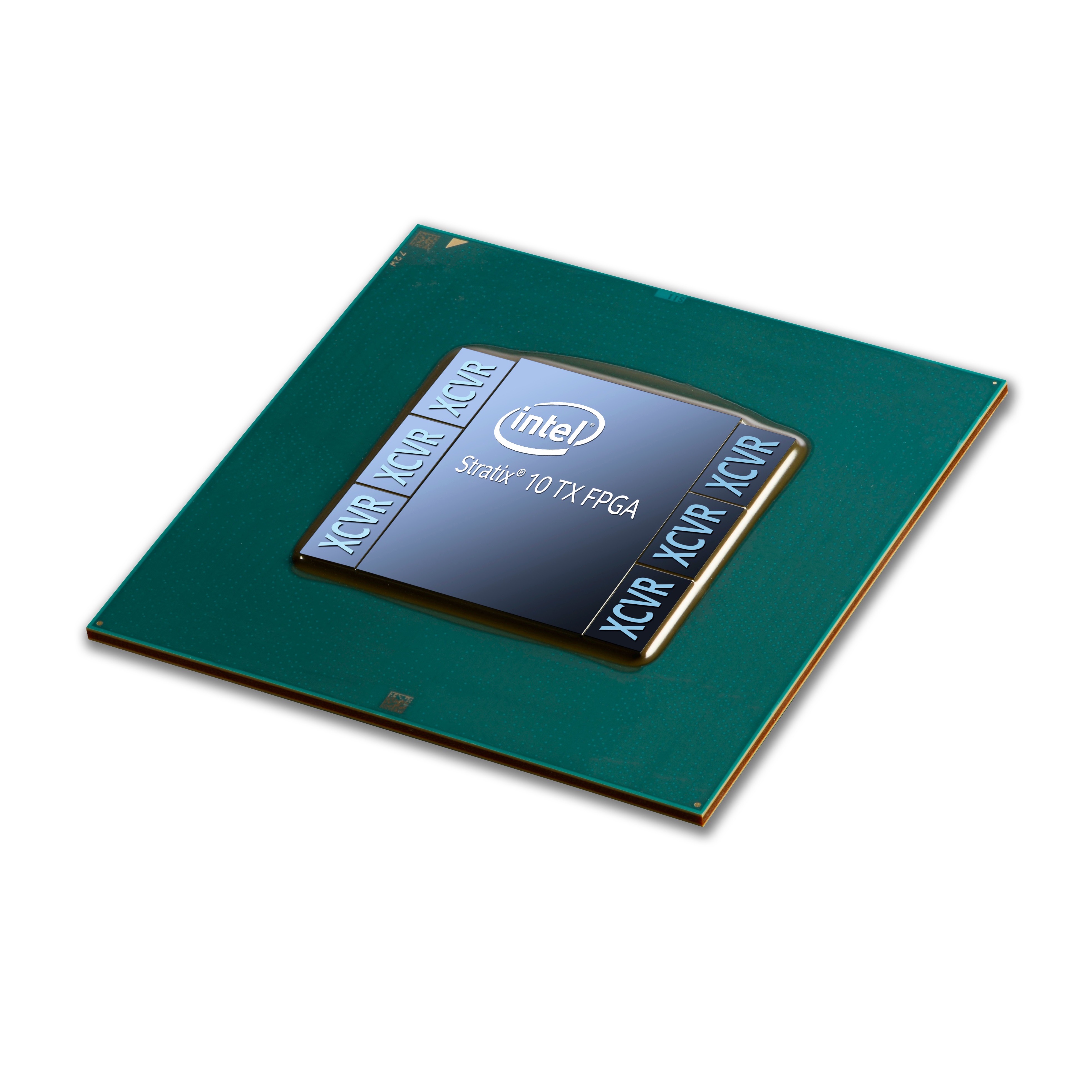

Это последнее письмо меня действительно удивило и заинтересовало. Альтера анонсирует новое поколение FPGA Stratix 10, которые будет выпускаться по технологии Intel’s 14 nm Tri-Gate.

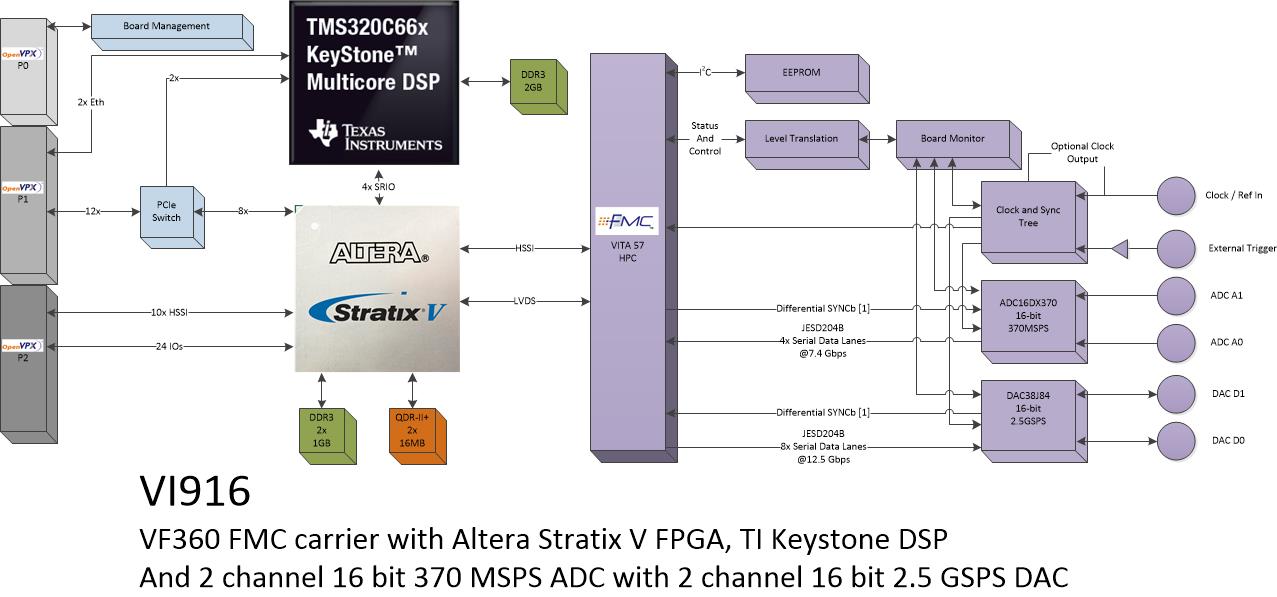

В серии Stratix 10 будет несколько вариантов:

1) Stratix 10 GT для ультра-скоростной обработки и передачи данных на скоростях до 56Gbps.

2) Stratix 10 GX — видимо что-то похожее (?) на GT, только скорости поменьше, до 32 Gbps.

3) Stratix 10 SX SoCs — содержит встроенный четырехядерный, 64-х битный процессор ARM (64 bit quad-core ARM Cortex-A53 processor).

Вот последний вариант с ARM мне кажется очень интересным.

В принципе у Альтеры ARM процессоры уже были в чипах средних серий Arria 10 SX, Arria V ST, Arria V SX, а так же в так называемых «low-cost» сериях Cyclone V SE/ST/SX.

Тут еще одна вещь примечательна.

К серии Stratix компания Альтера уже давно продвигает технологию OpenCL. Идея этой технологии такая: программист пишет на C-подобном языке (считается, что его знают многие) как бы две программы:

- Первая — управляющая программа.

- Вторая — набор кернелов. Это такие, условно говоря, «подпрограммы», которые выполняют операции над блоком входных данных.

Например, нужно выполнить сжатие видеопотока. Очевидно, что часто выполняющиеся операции — это преобразование RGB блока в яркостный и цветоразностные, далее операция Forward DCT, квантизация, упаковка хаффманом. Вот видимо для каждого такого этапа можно написать на C-подобном языке свой kernel. Потом они компилируются в FPGA Stratix и могут быть загружены туда и выполнять параллельно вычисления над многими макроблоками изображения блоками одновременно.

В принципе OpenCL как-то поддерживается в видеокартах NVidia (правда говорят их реализация OpenCL пока еще менее производительна, чем их же аналогичная проприетарная технология NVIdia CUDA).

Ну вот похоже Альтера то же хочет работать на рынке высокопроизводительных вычислений с помощью OpenCL.

Раньше Альтера предлагала FPGA PCIe платы с поддержкой OpenCL для персональных компьютеров. Сейчас же OpenCL будет доступен прямо внутри Stratix 10 SX с 64х битным ARM. По моему это весьма круто. Вопрос конечно в цене. Сколько это чудо будет стоить? Пока на сайте альтеры цены нет.

Если бы у вас была плата с таким SoC, то какое бы устройство вы хотели бы реализовать в нем?

Intel ARM / FPGA Stratix 10 SoC — первая 14-нм FPGA

Intel начала тестировать Altera Stratix 10, 14-нм SoC, который объединяет 4 ядра Cortex-A53 с FPGA уровня Stratix V, используя при этом на 70% меньше энергии.

Впервые Altera анонсировала

Stratix 10 SX

еще в 2013 году, но SoC была отложена, и сейчас только начинается выборка.

Наряду с проблемой создания первой 14-нм FPGA, изготовленной по технологии Intel Tri-Gate с 14-нм технологическим процессом, развертывание также, вероятно, было отложено из-за недавнего приобретения Intel этого производителя чипов.

Теперь Intel заявляет, что SoC демонстрирует «самые значительные инновации в области ПЛИС за последние десять лет».

Stratix 10 ориентирован в первую очередь на центр обработки данных.

Тем не менее, SoC с поддержкой Linux, скорее всего, также окажется в основе встроенных технологий.

SoC будет ориентирован на «приложения с интенсивным использованием данных, начиная от центров обработки данных, сетевой инфраструктуры, облачных вычислений и радаров и систем обработки изображений», — говорит Intel.

Stratix 10

(щелкните изображение, чтобы увеличить)

Также имеется 1 МБ кэш-памяти второго уровня и 32 КБ для ввода-вывода.

Altera также перечисляет линию Stratix GX, в которой отсутствует подсистема ARM, но в остальном она идентична.

SoC SX и GX доступны в девяти различных SKU с различными уровнями логических элементов (LE), адаптивных логических модулей (ALM) и других счетчиков FPGA.

Они варьируются от 484 тыс. LE на SX 500 или GX 500 до более 4,4 млн на SX или GX 4500.

Кроме того, Altera упоминает семейство Stratix 10 GT, которое, как представляется, является будущим предложением.

Высококачественный GT поддерживает приемопередатчики с пропускной способностью до 56 Гбит / с.

Следующие заявления Intel, по-видимому, относятся к моделям ARX-ready SX.

Intel сравнивает Stratix 10 с FPGA Stratix V, но на самом деле он более сопоставим с

Cyclone V

с поддержкой Linux и более

мощным Arria 10 SoC

, которые аналогичным образом объединяют компоненты ARM Cortex и FPGA.

Фактически, Stratix 10 совместим по размерам с Arria 10, что рекомендуется для ранней разработки продуктов на основе Stratix 10.

По словам Intel, по сравнению с FPGA Stratix V, Stratix 10 потребляет на 70% меньше энергии, предлагая эквивалентную производительность с интеграцией до 5,5 миллионов логических элементов.

SoC обеспечивает вдвое большую производительность ядра и более чем в пять раз плотность по сравнению с предыдущим поколением, говорит производитель чипов.

Блок-схема подсистемы ARM Stratix 10 (слева) и блок DSP в режиме фиксированной точки стандартной точности

(нажмите на картинку, чтобы увеличить)

Stratix 10 отличается интеграцией системы в пакете (SiP) с памятью высокой пропускной способности (HBM2), которая обеспечивает высокую плотность межсоединений между ПЛИС и сопутствующим кристаллом.

По словам Intel, благодаря технологии HBM2 Stratix 10 может обрабатывать до 1 ТБ / с пропускной способности памяти.

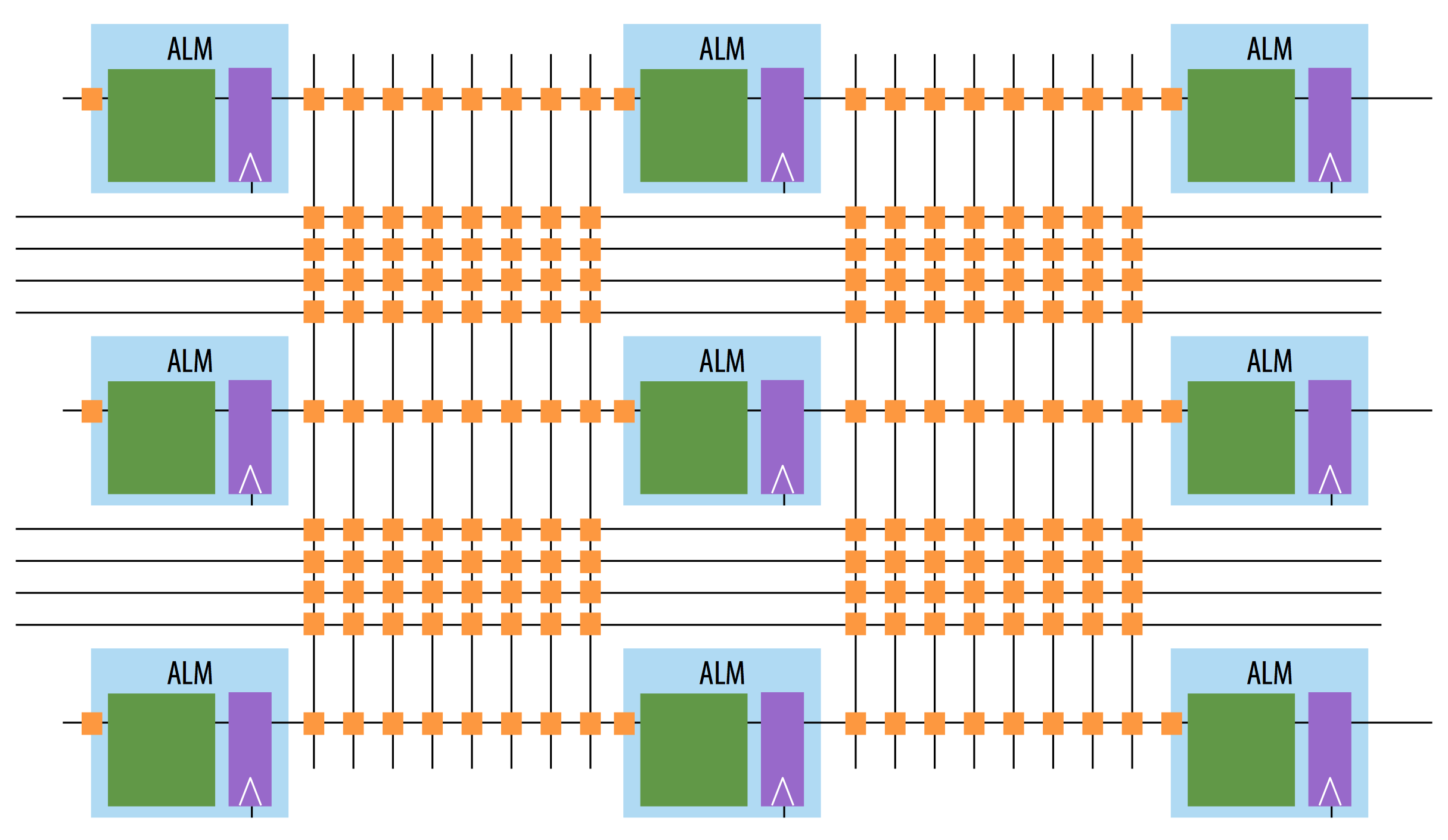

Благодаря архитектуре SoC «HyperFlex» каждый сегмент маршрутизации на устройстве имеет собственный связанный «Hyper-Register». Эти специализированные регистры также реализованы на входах всех функциональных блоков, таких как ALM, блоки встроенной памяти (M20K) и DSP. блоки.

Считается, что подход архитектуры «везде регистрируется» позволяет настраивать производительность, не требуя дополнительных ресурсов ALM, дополнительных изменений или усложнения места и маршрута проекта.

Кроме того, наличие гиперрегистрации, встроенной в межсоединение, помогает уменьшить перегрузку маршрутизации.

Stratix 10 интеграция памяти HyperFlex и HBM2 SiP (слева) и диаграмма, показывающая «регистры везде» в конструкции HyperFlex с Hyper-Registers

(нажмите на картинку, чтобы увеличить)

Архитектура HyperFlex включает в себя программируемый синтез тактового дерева, что обеспечивает улучшенное тактирование ядра.

Кроме того, в процессе проектирования «Hyper-Aware» добавлен инструмент быстрой пересылки и этап Hyper-Retimer, который поддерживает оптимизацию производительности после размещения и маршрутизации.

По словам Intel, Stratix 10 поддерживает до 144 трансиверов со скоростью передачи данных до 30 Гбит / с.

SoC поддерживает пропускную способность более 2,5 Тбит / с для последовательной памяти и более 2,3 Тбит / с для параллельных интерфейсов памяти, включая поддержку оперативной памяти DDR4 со скоростью до 2666 Мбит / с.

Функции безопасности управляются диспетчером защищенных устройств (SDM).

SDM создает унифицированную, безопасную систему управления для всего устройства и управляет конфигурацией, безопасностью устройства, ответами на отдельные события (SEU) и управлением питанием.

Stratix 10 против Zynq UltraScale + MPSoC

Stratix 10 напрямую конкурирует с 16-нм процессором Xilinx Zynq

UltraScale + MPSoC

, который аналогичным образом объединяет четыре ядра Cortex-A53 с высокопроизводительной FPGA, а также добавляет два микроконтроллера Cortex-R5 для управления в реальном времени.

Эта четырехъядерная версия недавно была запущена в производство в 16-нм и 20-нм моделях TSMC, а в следующем году появится двухъядерная

версия CG,

предназначенная для рынка встраиваемых систем.

Stratix 10 более прямо нацелен на центр обработки данных, отражая роль ПЛИС Altera в оборудовании инфраструктуры связи центра обработки данных, среди других приложений.

Intel рассматривает ПЛИС как способ эффективной обработки высокопараллельных рабочих нагрузок и огромного количества входных данных, с которыми сталкиваются центры обработки данных, когда они агрегируют данные IoT и обрабатывают огромные объемы мультимедийных данных, таких как видеочат.

ПЛИС имеют уникальную возможность перепрограммироваться в полевых условиях для обработки новых сценариев.

ПЛИС также сложнее разрабатывать, но благодаря интеграции ПЛИС с процессорами приложений — тенденция, которая началась с

Xilinx Zynq-7000

— они стали более доступными.

Linux является операционной системой по умолчанию в Altera

SoC Embedded Design Suite

(EDS), которая включает в себя ARM Development Studio 5 (DS-5) и Altera OpenCL SDK.

Существует также программное обеспечение для проектирования Altera Quartus Prime FPGA, которое включает в себя новый механизм Spectra-Q, оптимизированный для архитектуры HyperFlex и потока проектирования Hyper-Aware, который обещает в 8 раз быстрее компиляции, чем предыдущие компиляторы Quartus.

Аномалия продажи Intel ARM-проектов, скорее всего, будет временной, поскольку исполнительный директор Intel Брайан Крзанич ранее заявил, что планирует объединить ПЛИС Altera с чипами Intel x86 как на рынке IoT, так и в центре обработки данных.

В центре обработки данных ядра ARM предположительно будут заменены на Xeons, а в пространстве IoT — на атомы.

Эти изменения, вероятно, потребуют времени, поэтому в ближайшей перспективе Intel станет дилером ARM в высшей лиге.

Дополнительная информация

Stratix 10 сейчас пробует.

Дополнительную информацию можно найти на

странице продукта

Intel / Altera

Stratix 10

.

Intel начала испытания Altera Stratix 10 ARM Cortex A53 + FPGA SoC

Intel купил Altera в прошлом году, а это значит ,что теперь Intel пришел и в FPGA бизнес, компания недавно объявила , что они начали предоставлять образцы Startix 10 SoC , изготовленные с использованием Intel 14 нм tri-gate . Интересно, что помимо FPGA , SoC также включает в себя четыре ядра ARM Cortex A53.

Intel / Altera Stratix ключ 10 SoC особенности и технические характеристики:

- Процессор — Четырехъядерный процессор ARM Cortex-A53 MP ядра до 1,5 ГГц

- Ядро для логических операций — 1 ГГц

- Плотность — 500K LE — 5.5M LE

- Встроенная память — 229 Мб

- До 11,520 18 х 19 Мультипликаторов

- До 144 трансиверов на 30 Гбит

- Устройства памяти Поддерживаемые — DDR4 SDRAM @ 1333 МГц, DDR3 SDRAM @ 1066 МГц, LPDDR3 @ 800 МГц, RLDRAM 3 @ 1200 МГц, QDR SRAM IV @ 1066 МГц, QDR II + SRAM @ 633 МГц, Cube Hybrid Memory

- Жесткий протокол IP — 3 EMACS, PCI Express Gen3 X 8, 10 / 40G BaseKR- для прямого исправления ошибок (FEC), Подуровень физического кодирования (PCS)

- Безопасность — AES-256 / SHA-256 bitsream шифрование / аутентификация, физическая функция (ППУ), ECDSA 256/384 аутентификация загрузочного кода, многофакторный ключ с многоуровневой иерархией, защита от атак со стороны канала.

По сравнению с предыдущим поколением FPGA (Stratix V), Intel утверждает, что новое устройство в два раза превышает производительность ядра, снижение энергопотребления до 70%, до 10 TFLOPS для значений с плавающей запятой DSP, и до 1 Тбит пропускной способности встроенной памяти с высокой пропускной способностью (HBM2) в-пакете.

Новая FPGA ориентирована на обработку данных и сетевых инфраструктур, которые требуют высокой пропускной способности, несколько протоколов и поддержку схем модуляции, с высоким соотношением производительности на ватт.

Вы найдете более подробную информацию о Altera Stratix странице 10 FPGA.

Благодарим сайт cnx-software.com за предоставленную информацию

Оригинал статьи тут

Система питания ПЛИС ALTERA ARRIA 10 FPGA и ARRIA 10 SOC: проверенные решения для управления питанием

19 Июл 2017Автор статьи

Афшин Одабай (Afshin Odabaee)

(Опубликовано в журнале «Вестник Электроники» №1 2016)

Скачать статью в формате PDF (267 КБ)

Введение

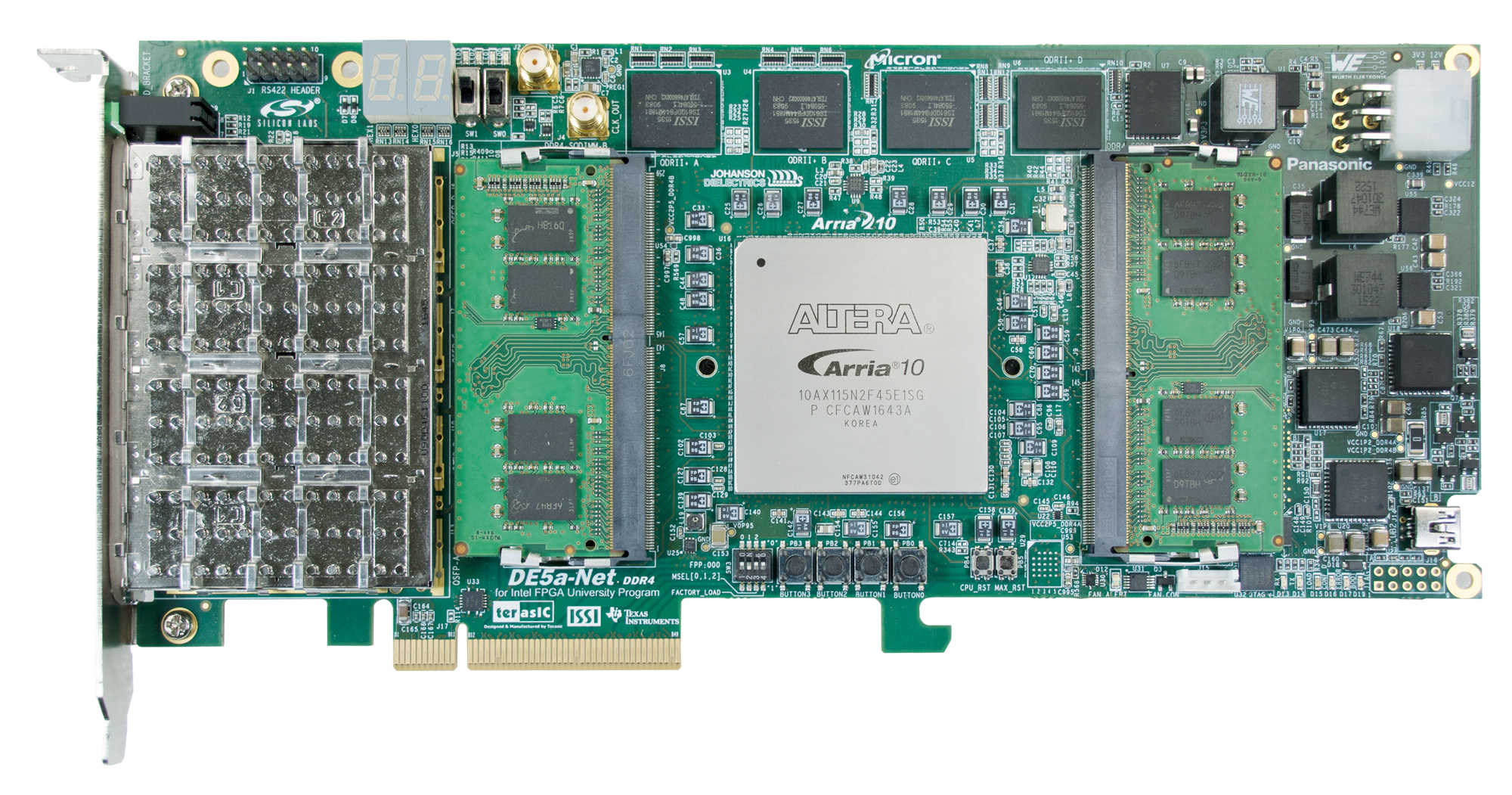

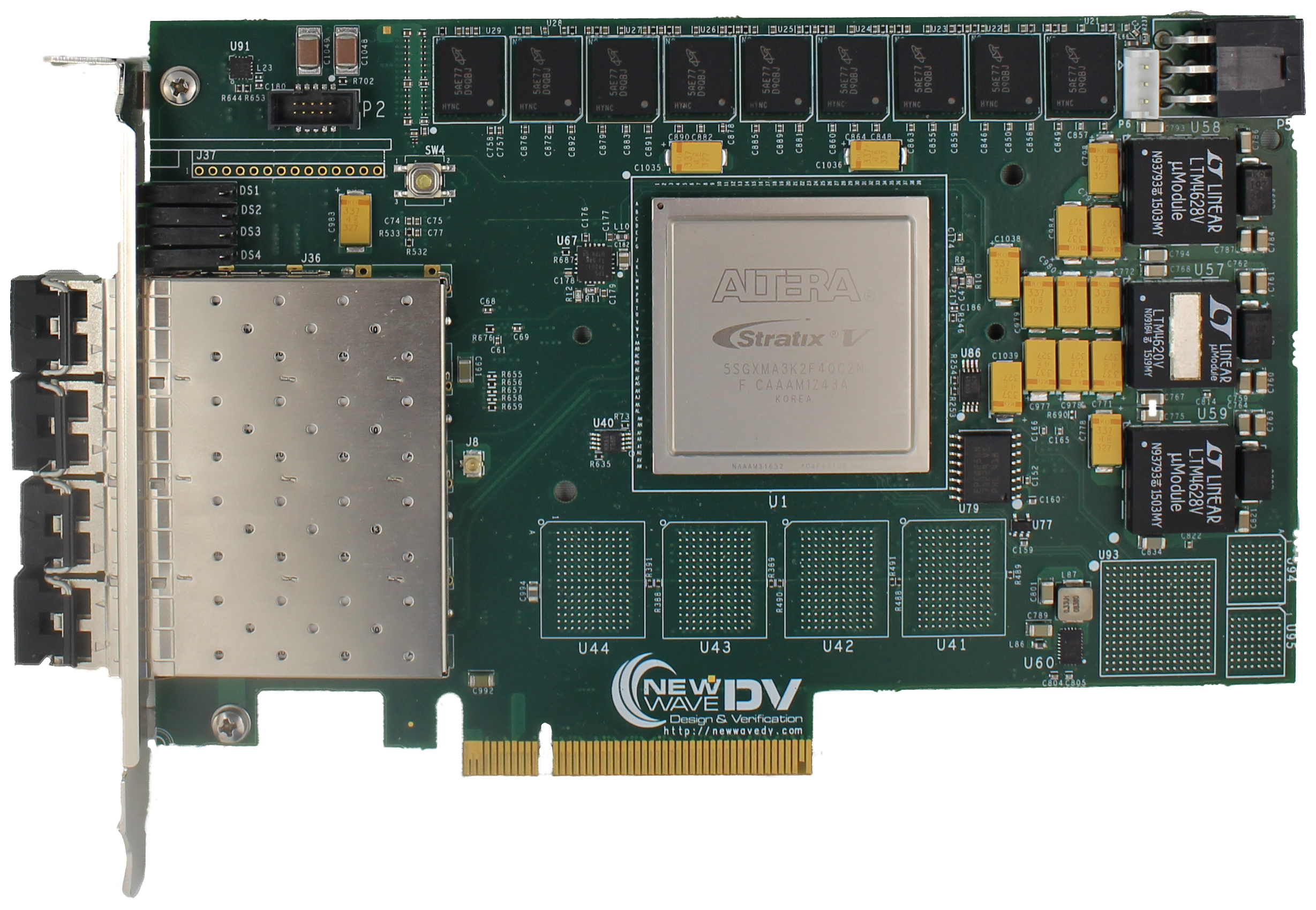

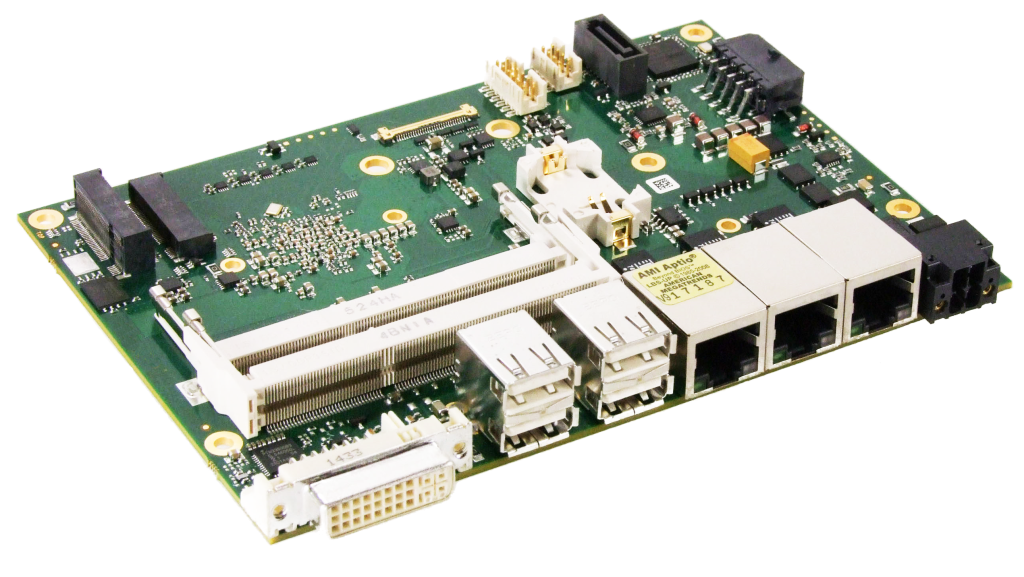

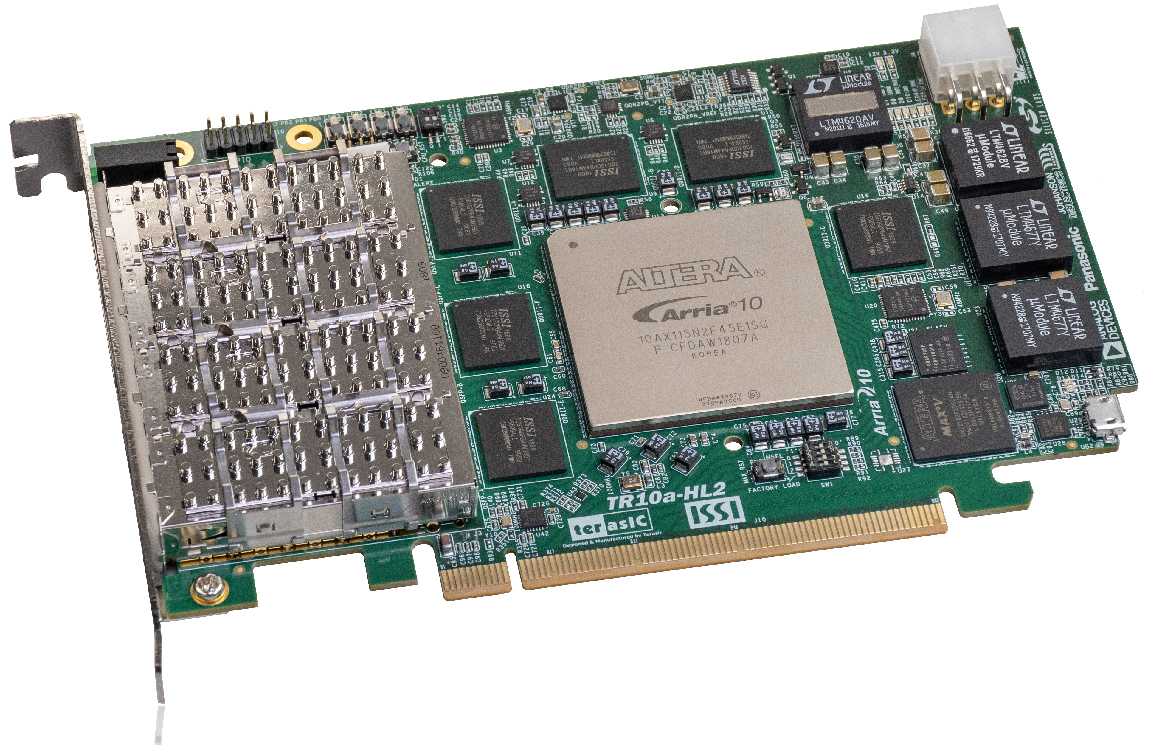

Наборы для тестирования ПЛИС позволяют разработчикам систем выполнять оценку ПЛИС, не создавая собственной системы. На рис. 1 и 2 представлены платы разработки, предназначенные для выпускаемых компанией Altera новых 20-нм ПЛИС — Arria 10 FPGA и Arria 10 SoC. Эти платы, испытанные и проверенные компанией Altera, являются примером профессионального проектирования, обеспечивающего целостность сигналов и эффективную систему управления питанием.

1 и 2 представлены платы разработки, предназначенные для выпускаемых компанией Altera новых 20-нм ПЛИС — Arria 10 FPGA и Arria 10 SoC. Эти платы, испытанные и проверенные компанией Altera, являются примером профессионального проектирования, обеспечивающего целостность сигналов и эффективную систему управления питанием.

Рис. 1. Демонстрационная плата Arria 10 GX FPGA

Рис. 2. Демонстрационная плата Arria 10 SoC

Управление питанием ПЛИС

Для достижения оптимальной производительности разработчикам необходимо тщательно выбирать решения для системы питания ПЛИС последнего поколения, которой и является Arria 10. Хорошо продуманная система питания может значительно уменьшить размер печатной платы, ее вес и сложность, а также снизить затраты энергии на ее охлаждение. Например, питание ядра Arria 10 (0,95 В, 105 A) может быть обеспечено импульсным DC/DC-преобразователем, имеющим ряд функций, позволяющих добиться максимального энергосбережения системы:

- Интегрированный в DC/DC-преобразователь 6-битный параллельный интерфейс VID в сочетании с подсистемой SmartVID позволяет уменьшить количество энергии, потребляемой ПЛИС, как в статическом, так и в динамическом режиме.

- Чрезвычайно малое значение сопротивления по постоянному току (DCR) датчика тока DC/DC-преобразователя улучшает эффективность и минимизирует потери мощности на индуктивности, а температурная компенсация отслеживает ее нагрев.

В таблице 1 представлен перечень основных шин питания (производства компании Linear Technology), используемых в отладочной плате Arria 10 — GX FPGA. Для ознакомления с полным перечнем источников, применяемых в данных отладочных платах, перейдите по ссылке www.linear.com/altera и выберите раздел Arria.

Таблица 1. Перечень элементов, использованных для построения системы питания демонстрационной платы Arria 10 GX FPGA

Моделирование системы питания с помощью LTpowerPlanner и LTpowerCAD

Как быть, если требования к цепям питания вашего устройства иные, чем в используемом вами наборе для разработки? В таких случаях используйте средства разработки LTpowerPlanner и LTpowerCAD. Данные утилиты позволяют создавать и оптимизировать собственные цепи питания для системы. Просто начните с решений, примененных в наборе разработки, а затем с легкостью изменяйте блоки цепей питания в соответствии с имеющимися требованиями и задачами, определяйте КПД и потери, находите решение для каждого отдельного случая. Система питания для отладочного набора Arria 10 GX FPGA была смоделирована и разработана с помощью данных утилит (рис. 3). Утилита LTpowerPlanner и ее более мощная модификация — LTpowerCAD находятся в свободном доступе, их можно загрузить на www.linear.com/ltpowercad.

Просто начните с решений, примененных в наборе разработки, а затем с легкостью изменяйте блоки цепей питания в соответствии с имеющимися требованиями и задачами, определяйте КПД и потери, находите решение для каждого отдельного случая. Система питания для отладочного набора Arria 10 GX FPGA была смоделирована и разработана с помощью данных утилит (рис. 3). Утилита LTpowerPlanner и ее более мощная модификация — LTpowerCAD находятся в свободном доступе, их можно загрузить на www.linear.com/ltpowercad.

Рис. 3. Схема питания для демонстрационной платы Arria 10 GX FPGA, смоделированная с помощью утилиты LTpowePlanner

Руководства и другие вспомогательные материалы, предназначенные для разработки систем с использованием ПЛИС производства компании Altera, вы можете найти по ссылке www.linear.com/altera.

Комментарий специалиста

Башмаков Павел, инженер по внедрению PT Electronics, [email protected]

На протяжении многих лет компания Linear Technology (LTC) тесно сотрудничает с ведущими производителями программируемых логических интегральных схем (ПЛИС), чтобы обеспечить разработчиков высокоэффективными источниками питания для самых чувствительных систем. В портфолио Linear Technology, Вы сможете найти современные и проверенные решения для любого семейства ПЛИС, а уникальные утилиты LTpowerPlanner и LTpowerCAD сделают процесс разработки максимально простым и эффективным.

В портфолио Linear Technology, Вы сможете найти современные и проверенные решения для любого семейства ПЛИС, а уникальные утилиты LTpowerPlanner и LTpowerCAD сделают процесс разработки максимально простым и эффективным.

Обновления продуктов Ссылки по теме ► Платы FPGA Руководство по выбору ► FMC Руководство по выбору модулей ► 10 г / 40 г Эталонный дизайн Ethernet / PCI Express Gen3 | HTG-STX10: платформа разработки Intel / Altera Stratix 10 Заселены одним

Intel / Altera Stratix 10 GX / SX 1650, 2100, 2500 или 2800 FPGA,

HTG-STX10 обеспечивает доступ к широкому диапазону плотностей затворов FPGA,

Ввод / вывод и память для множества различных программируемых приложений. Архитектура HTG-STX10 обеспечивает простую и универсальную функциональность расширение за счет трех совместимых с Vita 57.4 High-Pin-Count Коннекторы FPGA Mezzanine Card (FMC +). Порты FMC + обеспечивают доступ к всего 240 входов / выходов LVDS FPGA и 72 последовательных трансивера GXT. Широкий выбор Доступны дочерние карты Vita57.1 FMC и Vita57.4 FMC + для сопряжения с HTG-STX10. платформа для разных приложений. HTG-STX10 поддерживается одним 72-битным разъемом ECC DDR4 SODIMM, обеспечивающим доступ к 16 ГБ Память SDRAM.Плата также поддерживается HiTech Global 4GB. Модуль гибридного куба памяти (HMC) FMC + для высокопроизводительной последовательной памяти. HTG-STX10 можно использовать в режиме PCI Express и автономном режиме и питание через 6-контактный Molex Разъем PCIe. Поддерживаемые устройства:

|

|

Intel выпускает ПЛИС Stratix 10 NX, ориентированные на рабочие нагрузки ИИ

Сегодня Intel представила свою первую FPGA, оптимизированную для искусственного интеллекта, Stratix 10 NX, которая имеет расширенные блоки AI Tensor (30 умножителей и 30 накопителей), встроенную память HBM и сеть с высокой пропускной способностью. В новом чипе по-прежнему используется архитектура чиплетов Intel, а часть микросхемы FPGA создана с использованием 14-нм технологии Intel.

В новом чипе по-прежнему используется архитектура чиплетов Intel, а часть микросхемы FPGA создана с использованием 14-нм технологии Intel.

Intel сообщает, что новая FPGA обеспечит до 15 раз больше вычислений INT8, чем Stratix 10 MX, представленный в конце 2017 года и чей блок DSP имел только два умножителя и два аккумулятора. Новый чип также оснащен «приемопередатчиками PAM4 емкостью до 57,8 Гбайт и жесткими блоками Intel Ethernet для обеспечения высокой эффективности». По словам Intel, Stratix 10 NX будет доступен в конце этого года.

«Наиболее разрушительной тенденцией является экспоненциальное увеличение размера и сложности модели ИИ», — сказал Дэвид Мур, корпоративный вице-президент, GM, группа программируемых решений, Data Platforms Group, Intel, на предварительном брифинге для СМИ. «Мы наблюдаем, что сложность модели искусственного интеллекта удваивается примерно каждые три с половиной месяца или в 10 раз в год. Таким образом, [он] приближается к десяткам миллиардов параметров и выше в самых больших моделях трансформаторов и моделях трансформаторов следующего поколения, таких как BERT и GPT ».

«Наш текущий вычислительный блок (MX) действительно предназначен для вычислений общего назначения.Таким образом, обеспечивается широкий уровень гибкости, позволяющий удовлетворить строгие требования в отношении различных приложений обработки сигналов, операций и точности [требований]. Конструкция блока тензора AI ориентирована на ускорение приложений AI, оптимизацию для эффективных тензорных конвейеров и пониженную точность, целочисленные форматы и форматы с плавающей запятой, обычно используемые в пространстве AI. Эти нововведения позволяют нам в 15 раз увеличить объем вычислений на той же площади, что и у нашего стандартного вычислительного блока DSP », — сказал Мур.

Ожидается, что ПЛИС будут играть растущую роль в качестве недорогих высокопроизводительных устройств в более специализированных нишах приложений.Среди преимуществ FPGA — возможность реализации обработки с малой задержкой и снижение затрат, связанных с неиспользуемыми микросхемами в ЦП общего назначения. Давно преследуемые репутацией сложного в программировании / разработке, новые инструменты несколько упрощают разработку FPGA. Надежды на то, что FPGA приведут к более общим реконфигурируемым системам, пока не оправдались.

Давно преследуемые репутацией сложного в программировании / разработке, новые инструменты несколько упрощают разработку FPGA. Надежды на то, что FPGA приведут к более общим реконфигурируемым системам, пока не оправдались.

«Обычно мы видим, что ПЛИС отличаются в приложениях реального времени с небольшими партиями. Таким образом, гибкость ПЛИС и настраиваемая иерархия памяти позволяют разработчикам действительно настраивать свои конструкции для создания оптимизированных решений с малой задержкой », — сказал Мур, который привел в качестве примеров обнаружение мошенничества и прием видеоданных в приложениях для умных городов.

Нацелившись на Nvidia, Intel заявляет, что ее устройство Stratix 10 NX в 2,3 раза быстрее графических процессоров Nvidia V100 для пакетной обработки BERT, в 9,5 раза быстрее при пакетной обработке LSTM и в 3,8 раза быстрее при пакетной обработке ResNet50. (См. Слайд ниже)

В Intel сейчас полным ходом идет движение к гетерогенной архитектуре. Мур сказал: «Очевидно, что сообщества разработчиков Xeon, AI и FPGA объединяются для решения разнородных вычислительных задач. В центре нашего внимания не только инструменты для интеграции оборудования и программного обеспечения, но и интеграция этих инструментов из стандартных библиотек и фреймворков для беспрепятственной поддержки разработки приложений.”

Мур сказал: «Очевидно, что сообщества разработчиков Xeon, AI и FPGA объединяются для решения разнородных вычислительных задач. В центре нашего внимания не только инструменты для интеграции оборудования и программного обеспечения, но и интеграция этих инструментов из стандартных библиотек и фреймворков для беспрепятственной поддержки разработки приложений.”

Intel делает большую ставку на oneAPI — основанную на стандартах унифицированную модель программирования, которую она продвигает, — чтобы облегчить интеграцию разнородных платформ Xeon с различными ускорителями, такими как FPGA.

Отвечая на вопрос о том, чем NX отличается от MX и как это связано с разработкой Intel FPGA, проделанной с помощью Microsoft Project Brainwave *, Мур охарактеризовал NX как эволюцию от MX и Microsoft, а не как нечто совершенно иное.

В последние годы Intel, конечно, приобрела несколько компаний-ускорителей и технологий, в том числе совсем недавно Habana Labs.

Отвечая на вопрос о планах в отношении Гаваны во время брифинга, Лиза Спелман, корпоративный вице-президент и генеральный менеджер Intel, Xeon and Memory Group, сказала: «Гавана сосредоточена на обучении ИИ или рабочей нагрузке по логическим выводам. Наша математика и наши расчеты совокупной стоимости владения показывают, когда вы смотрите на поток рабочей нагрузки, если ИИ становится [достаточно высоким] процентом рабочей нагрузки, ваша экономика может улучшиться за счет перехода к ускорению или выделенному ускорению в дополнение к базовому процессору. [Это] должно зависеть от размера рабочей нагрузки, объема данных, которые вы пытаетесь обработать с помощью функции обучения или вывода, а затем от потока рабочих нагрузок.

Наша математика и наши расчеты совокупной стоимости владения показывают, когда вы смотрите на поток рабочей нагрузки, если ИИ становится [достаточно высоким] процентом рабочей нагрузки, ваша экономика может улучшиться за счет перехода к ускорению или выделенному ускорению в дополнение к базовому процессору. [Это] должно зависеть от размера рабочей нагрузки, объема данных, которые вы пытаетесь обработать с помощью функции обучения или вывода, а затем от потока рабочих нагрузок.

«Есть такие, как, опять же, я упомянул рекомендательные системы, потому что поток рабочей нагрузки и способ, которым логический вывод встроен в ответ, ЦП на самом деле является очень естественным и наиболее вероятным местом для выполнения этих рабочих нагрузок. Если вы думаете [о других], потенциально обработка изображений в очень специфической среде обучения, ускоритель, такой как Habana, посвященный поставленной задаче, может оказаться лучшей моделью общей стоимости владения, даже если он используется для более узкой части проблема. ”

”

* Microsoft Project Brainwave:

«Project Brainwave — это платформа глубокого обучения для вывода ИИ в реальном времени в облаке и на периферии. Программный блок нейронной обработки (NPU), основанный на высокопроизводительной программируемой пользователем вентильной матрице (FPGA), ускоряет вывод глубоких нейронных сетей (DNN) с приложениями в области компьютерного зрения и обработки естественного языка. Project Brainwave преобразует вычисления, добавляя в процессоры взаимосвязанный и настраиваемый вычислительный уровень, состоящий из программируемого кремния.

«Например, в этой конфигурации FPGA удалось более чем на порядок улучшить задержку и пропускную способность RNN для Bing без пакетной обработки. За счет предоставления ИИ в реальном времени и сверхнизкой задержки без необходимости пакетной обработки накладные расходы и сложность программного обеспечения снижаются ». https://www.microsoft.com/en-us/research/project/project-brainwave/

Избыточный запас ПЛИС Intel® Stratix® 10 GX 280H FBGA-1760продается дешево 10 000 евро — Sky Blue Microsystems GmbH

Новинка | В оригинальной герметичной упаковке | Гарантия производителя | Избыток | 10 000 евро за штуку

Лучшая цена 10 000 долларов США | Пока есть запасы

Чип Intel® Stratix® 10 GX 280H FBGA-1760 FPGA поставляется с 28.Приемопередатчики со скоростью 3 Гбит / с и процессор ARM A53.

Intel® приобрела Altera® в 2015 году, поэтому эти FPGA ранее были известны как чип Altera® Stratix® 10 GX.

Эти FPGA оптимизированы для приложений, требующих максимальной пропускной способности приемопередатчика и производительности основной фабрики.

У нас есть избыток запасов, который мы были бы рады продать по отличной лучшей цене в размере 10 000 евро за штуку.

Все детали новые и находятся в оригинальной запечатанной упаковке. На них распространяется полная гарантия производителя.

Мы продаем модель Intel® Stratix® 10GX

- 1SX280HN2F43E2LG или

- 1S X 280 H N 2 F 43 E 2 L G.

Данная спецификация Intel® Stratix® разбита следующим образом:

| 1S | Stratix 10 |

| X | GX |

| 280 | 2800K логических элементов (2 800 000 LE) |

| H | H-Tile |

| N | 48 трансиверов |

| 2 | Класс скорости трансивера |

| F | FineLine BGA (FBGA) 1.Шаг 0 мм (тип корпуса) |

| 43 | 1760 контактов, 42,5 мм x 42,5 мм (код упаковки) |

| E | Расширенная рабочая температура, 0 ° C-100 ° C |

| 2 | Класс скорости коммутации ПЛИС |

| L | Низкое энергопотребление (фиксированное напряжение) |

| G | RoHS6 |

Свяжитесь с нами по лучшей цене, чтобы купить эти Intel® Stratix® 10 GX 280H FBGA-1760 ПЛИС, которые мы продаем за 10 000 долларов, пока их нет в наличии.

Intel®, Stratix® и Altera® являются зарегистрированными товарными знаками.

Данные продукта

Altera Stratix 10 FPGA — FPGA Familis

ПЛИС и SoCStratix 10 обеспечивают высочайшую производительность наряду с высочайшим уровнем системной интеграции. Узнайте больше об уникальных возможностях и революционных преимуществах, которые устройства Stratix 10 предоставляют для создания высокопроизводительных систем следующего поколения в широком спектре приложений, ниже.

ПЛИС Stratix 10 GX

ПЛИС Stratix 10 GX разработаны для удовлетворения требований к высокой производительности систем с высокой пропускной способностью с производительностью до 10 терафлопс с плавающей запятой и поддержкой приемопередатчиков до 28.3 Гбит / с для приложений «микросхема-модуль», «микросхема-микросхема» и объединительной платы.

Stratix 10 SX SoC FPGA

Stratix 10 SX SoC FPGA оснащены жесткой процессорной системой с 64-битным четырехъядерным процессором ARM * Cortex-A53, доступным во всех плотностях в дополнение ко всем функциям устройств Stratix 10 GX.

ПЛИС Stratix 10 TX

ПЛИС Stratix 10 TX обеспечивают самые передовые возможности приемопередатчиков в отрасли за счет комбинирования плит Н- и Е-приемопередатчиков. E-tile обеспечивает возможности двухрежимного трансивера, позволяя одному каналу трансивера работать со скоростью до 56 Гбит / с в режиме PAM-4 или 28.9 Гбит / с в режиме NRZ. ПЛИС Stratix 10 TX также поддерживают другие прорывные инновации вариантов Stratix GX и SX.

ПЛИС Stratix 10 MX

ПЛИС Stratix 10 MX сочетают в одном корпусе программируемость и гибкость ПЛИС и SoC Stratix 10 с трехмерной стековой памятью с высокой пропускной способностью 2 (HBM2). ПЛИС Stratix 10 MX поддерживают блоки H- и E-приемопередатчиков.

Stratix 10 DX FPGA

Stratix 10 DX FPGA — первые устройства FPGA, поддерживающие Ultra Path Interconnect (UPI) для прямого когерентного подключения к будущим избранным процессорам Xeon Scalable.Они включают интерфейс PCIe * Gen4 с конфигурацией до x16 со скоростью 16 ГТ / с и новый контроллер памяти для поддержки выбранной постоянной памяти Optane DC.

Stratix 10 NX FPGA

ПЛИС, оптимизированная для искусственного интеллекта, для приложений ускорения искусственного интеллекта (AI) с высокой пропускной способностью и малой задержкой. Stratix 10 NX FPGA обеспечивает ускоренное решение для вычислений AI с помощью вычислительных блоков, оптимизированных для AI, с пропускной способностью INT82 до 15 раз больше, чем у стандартного блока DSP Stratix 10 FPGA; в пакете 3D stacked HBM с высокой пропускной способностью DRAM; и до 57.Приемопередатчики 8G PAM4.

Новый Stratix 10 GX 10M FPGA

Самое лучшее в производстве программируемых вентильных матриц (FPGA) — это то, что вы можете сделать кремний очень большим. Природа повторяющейся конструкции блока может устранить проблемы, связанные с технологическим процессом, и в результате мы часто видим, что FPGA являются крупнейшими кремниевыми кристаллами, которые выходят на рынок для данного производственного процесса. Когда вы достигнете предела того, насколько большой вы можете сделать кусок кремния (известного как предел сетки), единственный способ стать больше — соединить этот кремний вместе.Сегодня Intel объявляет о выпуске своей последней «большой» FPGA, и это знаменательная веха в области технологии связи.

Одним из движущих сил этой отрасли является технология упаковки. Мы подробно рассмотрели такие элементы, как корпус TSMC 2.5D Chip-On-Wafer-On-Substrate (COWOS), используемый в графических процессорах, встроенный мост Intel Multi-Die Interconnect Bridge (EMIB), технологию стекирования, такую как FOVEROS, и по мере перехода на более мелкие Кремний на основе чиплетов, каждый из них будет иметь решающее значение для поиска наилучшего способа производства конечного чипа, который войдет в миллион систем.

Несмотря на лучшие диаграммы Intel о своей технологии EMIB, на которых показано множество кристаллов, соединенных вместе из нескольких различных технологических узлов, компания избежала одного серьезного препятствия. До этого момента все, что мы видели от EMIB, — это подключение одного высокомощного кристалла, такого как графический процессор, к маломощному кристаллу, например HBM. Одно из критических замечаний по поводу того, что только известные продукты Intel соединяют один кристалл высокой мощности и один кристалл с низким энергопотреблением, заключается в том, что соединение EMIB не было термически стабильным, чтобы выдерживать циклическое переключение питания между двумя кристаллами.

Один из макетов Intel того, как будущие процессоры могут выглядеть

При соединении двух кристаллов вместе в подложке, особенно высокомощного кристалла с переходными отверстиями или конструкции BGA, необходимо учитывать механические напряжения, особенно если задействованы разные металлы. Тепловое расширение и сжатие — критическая точка отказа, особенно при работе со встроенными конструкциями и конструкциями с длительным жизненным циклом. Не только расширение и сжатие металлов, но и при работе с органическими подложками, удерживающими упаковочную технологию, создание неразрывно тонкой подложки также серьезно увеличивает долгосрочные проблемы осуществимости, особенно если для соединения используется высокомощный кристалл.

С появлением новой FPGA Intel Stratix 10 GX 10M беспокойство, похоже, исчезло. Этот новый продукт, разработанный как большая ПЛИС для рынка прототипирования и эмуляции ASIC, сочетает в себе две большие ПЛИС с логическим элементом 5.1M и три соединения EMIB, создавая общий чип со средним TDP от 150 до 400 Вт с улучшенным охлаждением.

Всего 7 соединений EMIB, но три в середине являются вехой

Рынок прототипирования и эмуляции ASIC, несмотря на небольшую выручку на рынке (Intel заявила ~ 300-500 миллионов долларов в год), всегда требует все больше и больше FPGA, чтобы иметь возможность уместить все больше и больше своих проектов ASIC на как можно меньшем количестве. Максимально возможное количество ПЛИС для получения наиболее точных результатов.Эти микросхемы в конечном итоге работают на низкой частоте для точности, от 50 до 300 МГц, но Intel заявляет, что эта новая конструкция Stratix 10 GX 10M может легко заменить четыре ее старых ПЛИС GX 2800 с удвоением возможностей подключения и даже 40 % снижение мощности при той же рабочей нагрузке.

Конструкция FPGA основана на этих двух кристаллах логических элементов 5.1M, соединенных вместе с помощью трех соединений EMIB. Они используют протокол AIB, работающий на частоте более 1 ГГц, и образуют часть 25920 соединительных контактов на всем чипе, который имеет еще четыре соединения EMIB с трансиверами, как показано на схеме.

Имея 10,2 миллиона логических элементов, эта FPGA затмевает анонсированный в августе Xilinx VU19P, в котором было 9 миллионов элементов (8172k триггеров, 4086k LUT). Stratix 10 GX 10M также содержит 6912 элементов DSP и 48 выходов приемопередатчиков со скоростью 17,4 Гбит / с. Intel заявляет, что они разработаны в первую очередь для поддержки PCIe 3.0 / 4.0, и что FPGA поддерживает H-плитки для подключения клиентов, заинтересованных в нестандартных конструкциях.

Выпуск этого нового оборудования совпадает с мероприятием Intel FPGA Tech Event в Китае, который является одним из основных рынков для этого продукта.Intel заявляет, что оборудование уже используется ключевыми партнерами почти год (один из первых заказчиков находится в Китае), но сейчас оно находится в производстве для более широкого рынка. Что касается высоких требований Intel к своим 14-нанометровым компонентам, компания заявила, что объем не так уж велик для такого рода продуктов, и у них не будет никаких проблем. Компания (по крайней мере, компания, входящая в состав FPGA) объяснила, что использование EMIB таким образом означает, что их подход с двумя кристаллами способствует увеличению доходности.

Лично тот факт, что Intel связывает два высокомощных кристалла (от ~ 75 Вт до ~ 150 Вт каждый) вместе, используя несколько соединений EMIB, является ключевым шагом в продвижении технологии EMIB на более широкий рынок.С этим как доказательством концепции он прокладывает путь к лучшему дизайну ЦП с несколькими кристаллами, а также обещает EMIB (и Foveros) в будущих продуктах с дискретными графическими процессорами.

Статьи по теме

Stratix 10 SX в основе самого мощного ускорителя ПЛИС Intel

Корпорация Intel начала поставки новой платы ускорителя FPGA, основанной на высокопроизводительной Stratix 10 SX FPGA. Это устройство, известное как Programmable Accelerator Card D5005, является продолжением первого PAC производителя микросхем на базе Arria 10, который был представлен почти два года назад.Новый PAC станет первым в сервере Hewlett Packard Enterprise ProLiant DL380 Gen10.

D5005 построен в основном для серверов 2U, таких как вышеупомянутый ProLiant DL380, и требует двух слотов PCI-Express 3.0 x16. Лучшая в линейке Stratix 10 SX FPGA предлагает 2,8 миллиона логических элементов, а карта, на которой она установлена, поддерживает 32 ГБ памяти DDR4 и два сетевых интерфейса Ethernet 100 Гбит / с. Полностью укомплектованная, D5005 может потреблять до 215 Вт мощности, что соответствует уровню графических процессоров, хотя это на 10 Вт меньше первоначальной оценки Intel, когда она анонсировала карту в сентябре прошлого года.

В любом случае, 200 с лишним ватт относят D5005 к специализированным серверам, в данном случае к тем, которые выполняют важные рабочие нагрузки с большим объемом данных, такие как потоковая аналитика, финансовый риск и нормативная аналитика, перекодирование видео, сетевая безопасность и т. Д. и преобразование речи в текст. Intel также нацелена на более широкую категорию ИИ, хотя, вероятно, только для логических выводов в тех случаях, когда преимущества платформы FPGA по задержке могут дать явное преимущество.

Напротив, менее мощная карта Arria 10 потребляет всего 66 Вт и подключается к однослотовому интерфейсу PCIe на сервере высотой 1U.По всем параметрам старый PAC является менее производительным устройством, предлагая всего 1,1 миллиона логических модулей на Arria GX FPGA, один порт Ethernet 40 Гбит / с и максимум 8 ГБ памяти DDR4. Arria 10 PAC в основном нацелен на ускорение баз данных, финансирование торговли, геномику и обработку изображений.

Однако, по словам Патрика Дорси, вице-президента и генерального менеджера недавно созданной Networking Custom Logic Group (NCLG) в Intel, есть некоторые приложения, пересекающиеся с D5005, особенно в областях потоковой аналитики, обработки изображений и сетевой безопасности. .Он говорит, что все зависит от требований конкретного приложения и ограничений по мощности. В целом, Arria 10 PAC будет развертываться ближе к границе и более широко.

Дорси, однако, отмечает, что по производительности на ватт D5005 является явным победителем, поскольку выигрыш в вычислительной мощности более чем компенсируется более высокими требованиями к мощности. «Таким образом, даже несмотря на то, что мощность кажется в 3,5 раза выше, прирост производительности составляет порядка 10 раз», — говорит он. И, конечно же, если критерием вождения является абсолютная производительность, D5005 — очевидный выбор.

Например, сжатие изображений Lepton выполняется в два с половиной раза быстрее на D5005, чем на Arria 10 PAC. Так что, если вы можете работать с более высоким диапазоном мощности, это будет более экономичный выбор для таких приложений (более энергоэффективный и требуется меньше серверов). С другой стороны, если проблема в питании или если сервер также используется для других (без ускорения) целей, Arria 10 PAC, вероятно, будет лучшим вариантом.

Важным преимуществом D5005 является больший объем доступной памяти как на ПЛИС, так и в качестве внешней оперативной памяти DDR4.Таким образом, для преобразования речи в текст более емкая встроенная память важна для сокращения времени отклика, что является ключевым требованием для таких приложений. В качестве альтернативы, для перекодирования видео критическим фактором оказывается доступ к большему объему ОЗУ DDR4. Для анализа финансовых рисков критическими факторами являются как вычислительная мощность более крупной ПЛИС в виде большого количества математических вычислений, так и доступ к внутренней памяти.

D5005 поставляется с тем же стеком программного ускорения, который предлагается с Arria 10 PAC, обеспечивая общий интерфейс для разработчиков и позволяя повторно использовать код в продуктах PAC.В стек также входят библиотеки ускорения, драйверы, менеджер интерфейса FPGA, SDK для OpenCL и Quartus Prime. Последний представляет собой набор программных инструментов, разработанных Intel для разработки программируемой логики для ПЛИС. Хотя сегодня существует только два продукта PAC, а варианты использования ограничены тем, что было установлено за последние пару лет, этот общий стек станет намного более важным, если и когда портфель PAC расширится и продукты станут более широко развернутыми.

Ясно, что это именно то, что имеет в виду Intel.По словам Дорси, хотя D5005 изначально будет доступен только на HPE ProLiant DL380, в ближайшее время ожидается дополнительная поддержка OEM. Учитывая, что Arria 10 PAC в настоящее время продается на серверах Dell, Supermicro, Inspur и Fujitsu, мы довольно хорошо представляем, какие OEM-производители в конечном итоге будут сертифицированы для нового D5005.

Дорси также отмечает, что продукты PAC, поддерживающие слоты PCI-Express 4.0 и 5.0, уже находятся в разработке. Кроме того, в будущих предложениях PAC также будет использоваться Compute Express Link (CXL), собственное межсоединение Intel для ускорителей когерентного кэширования.«Очевидно, что у нас есть план развития, поскольку возможности Xeon и FPGA продолжают расти», — говорит Дорси.

Altera представляет инновации Stratix 10, обеспечивающие самые быстрые и высокопроизводительные ПЛИС и SoC в отрасли

ПЛИС и SoCStratix 10 используют революционную архитектуру матрицы ПЛИС HyperFlex ™ от Altera, основанную на 14-нм процессе Tri-Gate Intel ® , чтобы обеспечить в 2 раза более высокую производительность ядра по сравнению с ПЛИС предыдущего поколения. Сочетание высочайшей в отрасли производительности, самой высокой плотности FPGA с расширенными возможностями встроенной обработки, производительности вычислений с плавающей запятой на уровне графического процессора и интеграции гетерогенных 3D SiP позволяет клиентам Altera уникальным образом решать задачи проектирования в коммуникациях, центрах обработки данных, инфраструктуре Интернета вещей и военной сфере следующего поколения. и высокопроизводительные вычислительные системы.

«Возможности, которые мы предлагаем в Stratix 10 FPGA и SoC, действительно не имеют себе равных в отрасли, — сказал Дэнни Биран, старший вице-президент по маркетингу Altera. «Stratix 10 FPGA и SoC позволят нашим клиентам разрабатывать свои системы и вводить новшества способами, которые ранее были невозможны в FPGA».

Архитектура HyperFlex Подход «везде регистрируется»

ПЛИС Stratix 10 и SoC — первые устройства Altera, использующие новую архитектуру HyperFlex компании, наиболее значительную инновацию в области коммутационной архитектуры в индустрии FPGA за более чем десятилетие.Архитектура HyperFlex, наряду с преимуществом полного технологического узла благодаря 14-нм техпроцессу Intel Tri-Gate, обеспечивает двукратное увеличение логической частоты ядра по сравнению с конкурирующими высокопроизводительными ПЛИС следующего поколения.

Архитектура HyperFlex вводит регистры во всех основных сегментах маршрутизации межсоединений, позволяя ПЛИС Stratix 10 и SoC пользоваться преимуществами проверенных методов проектирования, повышающих производительность, таких как повторная синхронизация регистров, конвейерная обработка и другие методы оптимизации проектирования. Эти методы проектирования непрактичны в обычных архитектурах FPGA.Архитектура HyperFlex позволяет разработчикам устранять критические пути и задержки маршрутизации, а также быстро сокращать сроки своих проектов. Способность достичь в 2 раза более высокой производительности основной логики также позволяет значительно улучшить использование устройств и мощность за счет снижения потребности в очень широких трактах данных и других вызывающих перекосы конструкциях, требуемых конкурирующими архитектурами. Архитектура HyperFlex позволяет высокопроизводительным конструкциям работать с пониженным энергопотреблением до 70 процентов за счет снижения требований к логической области.Дополнительную информацию см. На сайте www.altera.com/hyperflex.

Новая эра гетерогенной интеграции трехмерных систем в корпусе

Все члены семейства Stratix 10 FPGA и SoC используют гетерогенную интеграцию 3D SiP для эффективной и экономичной интеграции монолитной основной матрицы FPGA с высокой плотностью (до 5.5 M логические элементы) с другими передовыми компонентами, тем самым увеличивая масштабируемость и гибкость Stratix 10 FPGA и SoC. Монолитная основная матрица максимизирует использование устройства и производительность, избегая проблем с подключением конкурирующих однородных устройств, которые используют несколько кристаллов FPGA для обеспечения более высокой плотности.Гетерогенная интеграция SiP в Altera обеспечивается за счет использования фирменной технологии Intel EMIB (Embedded Multi-die Interconnect Bridge), которая обеспечивает более высокую производительность, меньшую сложность, более низкую стоимость и улучшенную целостность сигнала по сравнению с подходами на основе интерпозера.

Первоначальные устройства Stratix 10 будут использовать EMIB для интеграции высокоскоростного последовательного трансивера и протокольных плиток с монолитной базовой логикой. Внедрение высокоскоростных протоколов и приемопередатчиков на основе гетерогенного подхода позволит Altera быстро поставлять варианты устройств Stratix 10, отвечающие растущим требованиям рынка.Например, использование гетерогенной интеграции 3D SiP дает устройствам Stratix 10 возможность поддерживать более высокие скорости приемопередатчиков (56 Гбит / с), новые форматы модуляции (PAM-4), стандарты связи (PCIe Gen4, Multi-Port Ethernet) и другие возможности. например, аналоговая или высокоскоростная память.

Все плотности семейства Stratix 10 будут доступны со встроенным 64-битным четырехъядерным процессором ARM ® Cortex ® -A53 с жесткой процессорной системой (HPS) с богатым набором функций периферийных устройств, включая управление системной памятью блок, контроллеры внешней памяти и высокоскоростные коммуникационные интерфейсы.Выпустив Stratix 10 SoC, Altera расширит свое лидерство в отрасли как единственный поставщик, предлагающий высококачественные SoC FPGA. Эта универсальная вычислительная платформа предлагает исключительную адаптируемость, производительность, энергоэффективность, системную интеграцию и производительность проектирования для широкого спектра высокопроизводительных приложений. Архитекторы могут использовать SoC Stratix 10 в высокопроизводительных системах для обеспечения виртуализации оборудования, добавляя при этом возможности управления и мониторинга, такие как предварительная обработка ускорения, удаленное обновление и отладка, настройка и мониторинг производительности системы.

Максимальная защита конструкции с комплексными возможностями безопасности

ПЛИС Stratix 10 и SoC обеспечат наиболее полные в отрасли возможности безопасности в высокопроизводительных ПЛИС. В его основе лежит инновационный Secure Design Manager (SDM), который обеспечивает секторальную аутентификацию и шифрование, многофакторную аутентификацию и технологию физически неклонируемых функций (PUF). Altera сотрудничает с Athena Group и IntrinsicID, чтобы предоставить ускорение шифрования мирового класса и PUF IP для Stratix 10 FPGA и SoC.Такой уровень безопасности делает Stratix 10 FPGA и SoC идеальным решением для использования в военной сфере, облачной безопасности и инфраструктуре Интернета вещей, где многоуровневая безопасность и разделенная защита IP имеют первостепенное значение.

Enpirion PowerSoC, оптимизированные для Stratix 10 FPGA и SoC

Stratix 10 FPGA и SoC поддерживаются портфелем решений Altera по питанию Enpirion PowerSoC. Enpirion PowerSoC оптимизированы для удовлетворения строгих требований к производительности и мощности, предлагая высокую эффективность при минимальной занимаемой площади.

Самое быстрое в отрасли завершение по времени для многомиллионных проектов LE

Новый механизм Spectra-Q Altera в программном обеспечении Quartus ® II предназначен для максимизации преимуществ производительности, мощности и экономии площади, которые обеспечивает архитектура HyperFlex, одновременно улучшая продуктивность разработчиков и время вывода на рынок ПЛИС и SoC Stratix 10. Программное обеспечение Quartus II расширяет лидерство Altera в области программного обеспечения за счет новых возможностей, которые обеспечат до 8-кратное улучшение времени компиляции, гибкость и ускорение ввода в проект, интеграцию по IP и поддержку OpenCL и других потоков проектирования более высокого уровня.Дополнительная информация о движке Spectra-Q доступна на сайте www.altera.com/spectraq.

Stratix 10 FPGA and SoC Технические характеристики:

- До 5,5 миллионов логических элементов в монолитном кристалле

- Интеграция гетерогенного 3D SiP объединяет матрицу FPGA с высокоскоростными трансиверами

- До 144 трансиверов обеспечивают 4-кратную пропускную способность последовательного интерфейса по сравнению с предыдущим поколением

- 64-битная четырехъядерная подсистема жесткого процессора ARM Cortex-A53, работающая до 1.5 ГГц

- Жесткий DSP с плавающей запятой обеспечивает выполнение операций с одинарной точностью до 10 терафлопс

- Secure Device Manager: комплексные высокопроизводительные возможности безопасности FPGA

- Лучшее в отрасли обнаружение и очистка одиночного события (SEU)

- Совместимый с посадочными местами путь миграции с ПЛИС Arria® 10 и SoC

- Энергетические решения Altera Enpirion обеспечивают максимальную энергоэффективность и экономию площади платы

- техпроцесс Intel 14 нм Tri-Gate

Доступность

Заказчики могут начать работу над своими проектами Stratix 10 уже сегодня, используя инструменты оценки производительности Fast Forward Compile.Инженерные образцы Stratix 10 FPGA и SoC будут доступны осенью 2015 года. Разработчики встроенного программного обеспечения могут использовать виртуальные платформы SoC от Mentor Graphics для ускорения разработки встроенного программного обеспечения Stratix 10 SoC. Для получения дополнительной информации о Stratix 10 FPGA и SoC обратитесь к местному торговому представителю Altera или посетите сайт www.altera.com/stratix10.

Заявление о перспективах

Этот пресс-релиз содержит прогнозные заявления в отношении ПЛИС Stratix 10 и SoC, а также о наличии инженерных образцов, созданных в соответствии с положениями безопасной гавани Закона о реформе судебных разбирательств по частным ценным бумагам 1995 года.Инвесторы предупреждаются, что прогнозные заявления связаны с рисками и неопределенностью, которые могут привести к тому, что фактические результаты будут отличаться от ожидаемых в настоящее время, как это обсуждается в документах Комиссии по ценным бумагам и биржам Altera, копии которых размещены на веб-сайте Altera и доступны в компании без плата.

Об Altera

Программируемые решения Altera® позволяют разработчикам электронных систем быстро и экономично вводить новшества, дифференцировать и выигрывать на своих рынках.Altera предлагает FPGA, SoC, продукты CPLD и дополнительные технологии, такие как power solutions , для предоставления ценных решений клиентам по всему миру. Посетите Altera на сайте www.altera.com.

Слова и логотипы ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS и STRATIX являются товарными знаками корпорации Altera и зарегистрированы в Бюро по патентам и товарным знакам США и в других странах. Все остальные слова и логотипы, обозначенные как товарные знаки или знаки обслуживания, являются собственностью их владельцев, как описано на сайте www.altera.com/legal.

Контактное лицо редактора:

Стив Габриэль

Altera Corporation

(408) 544-6846

[электронная почта защищена]

Фото — http://photos.prnewswire.com/prnh/20150605/221205

Logo — http: //photos.

6

6 4) порты, поддерживающие в общей сложности 240 LVDS входов / выходов и

72 последовательных трансивера

4) порты, поддерживающие в общей сложности 240 LVDS входов / выходов и

72 последовательных трансивера