Прототипирование ASIC на FPGA / Хабр

Разработка микросхем дело сложное, дорогое и долгое. И цена любой ошибки крайне велика. После изготовления кристалла патчами и обновлениями уже ничего не исправить. Поэтому к проверке проектируемых схем на этапе разработки подходят особенно скрупулёзно. Для каждого функционального блока пишутся блочные тесты во всех рабочих и не рабочих режимах. После интеграции блока в общую схему проводятся системные тесты, как этот блок работает составе системы. Все тесты постоянно крутятся в регрессионном тестировании. Даже есть неформальный признак более менее приемлемого уровня тестирования – когда объем кода тестов в 10 раз больше объема кода тестируемого блока. Но все эти тесты не дают ощущения, что схема жизнеспособна, так как любое моделирование это поведение схемы на протяжении сотен миллисекунд максимум. А в жизни схема должна отработать сотни тысяч часов. Однажды я искал сбой, когда на 1 Гбайт переданной информации терялись 1 или 2 байта и никакие функциональные тесты эту проблему не обнаруживали.

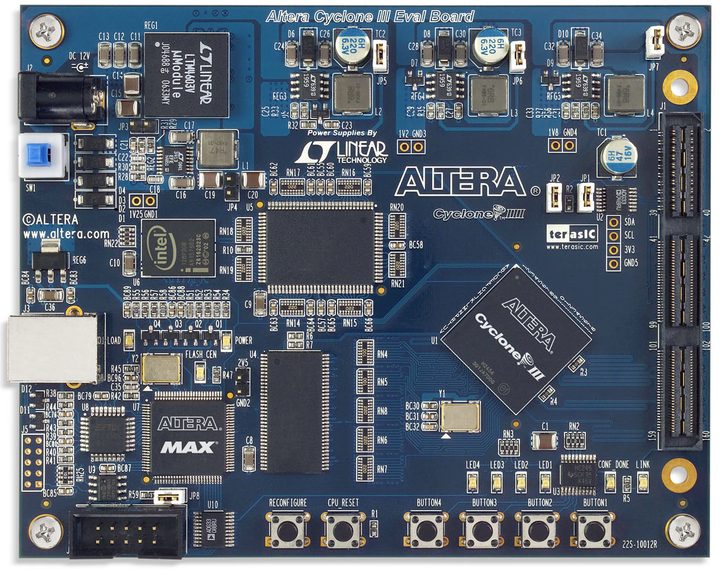

Прототипирование будущих микросхем на FPGA это единственный способ проверить как работает схема на реальных задачах в более менее реальном масштабе времени. Прототип позволяет отладить софт, получить первоначальные характеристики производительности и многое другое. Современные FPGA обладают достаточно большим объемом ресурсов для этих задачи. Например, вы можете сами на плате с FPGA за 300$

реализовать полноценный компьютер с процессором Intel 80862004 год

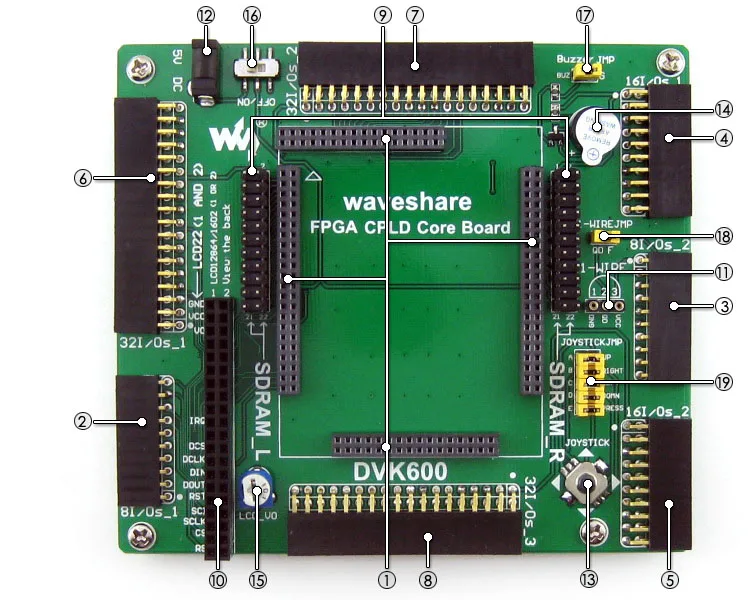

К сожалению самого первого прототипа в залежах нашего шкафа со скелетами найти не удалось, но это была небольшая платка на базе Xilinx Spartan3-400 (XC3S400). 400 означает число тысяч эквивалентах вентилей, которые доступны разработчику для создания своей схемы. Цена платки составляла примерно 50$ и позволяла реализовать в ней простой 8-ми битный микроконтроллер со всей памятью и на частоте 40 МГц. Прототипирование заключалось в том, что разработанный микроконтроллер на ней поморгал светодиодом.

Прототипирование заключалось в том, что разработанный микроконтроллер на ней поморгал светодиодом.

2005 год

Специальная плата для прототипа уже разрабатывалась не как эксперимент, а как осмысленный этап проекта. Применялась уже FPGA Xilinx Spartan3-1000. Т.е. нам уже был доступен 1 млн вентилей, и проектируемый микроконтроллер работал на своей макимальной частоте 48 МГц. И именно на этой плате я ловил те самые 2 потерянных байта на гигабайт. Цена платы составляла примерно 200$.

2007 год

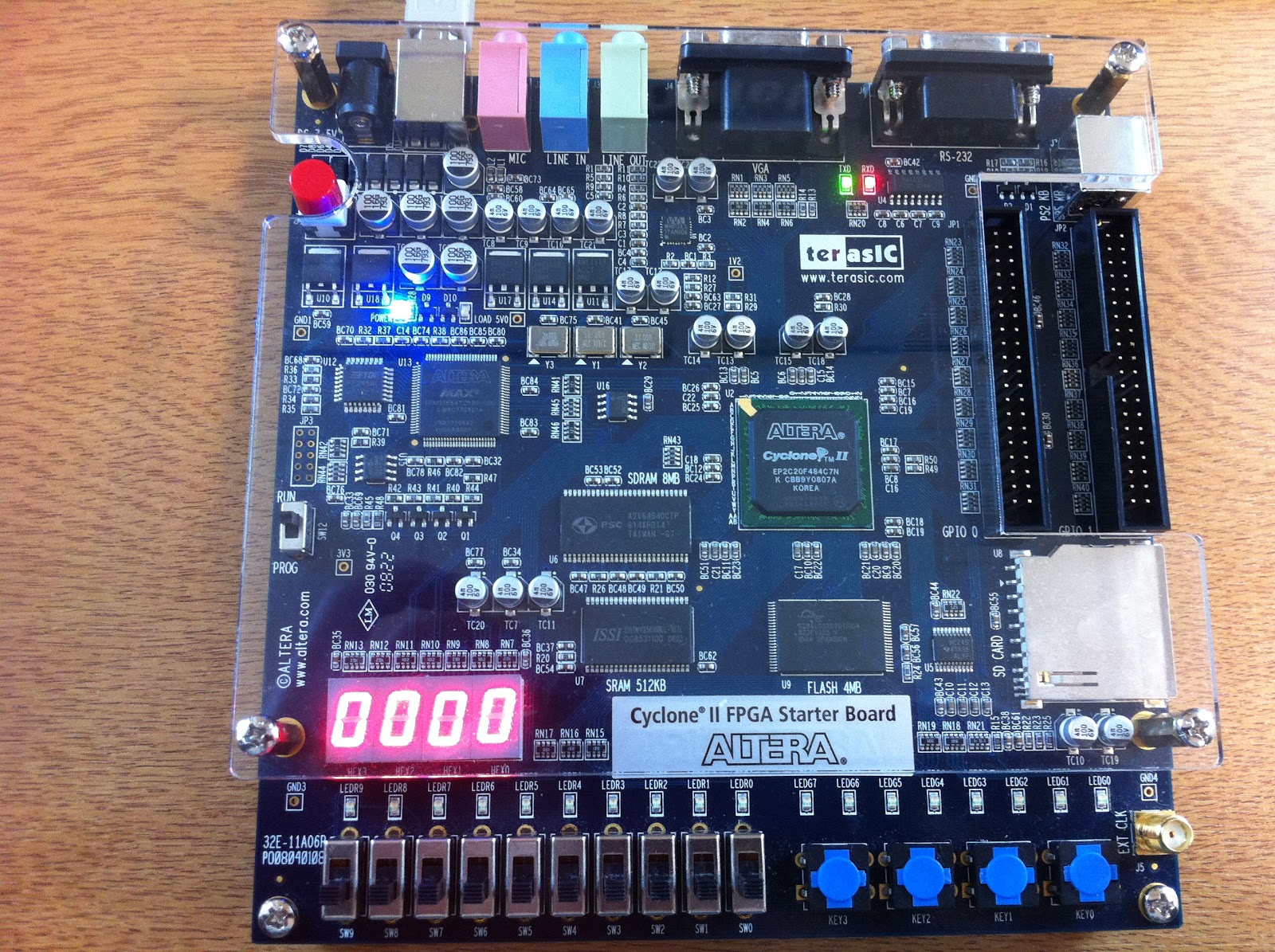

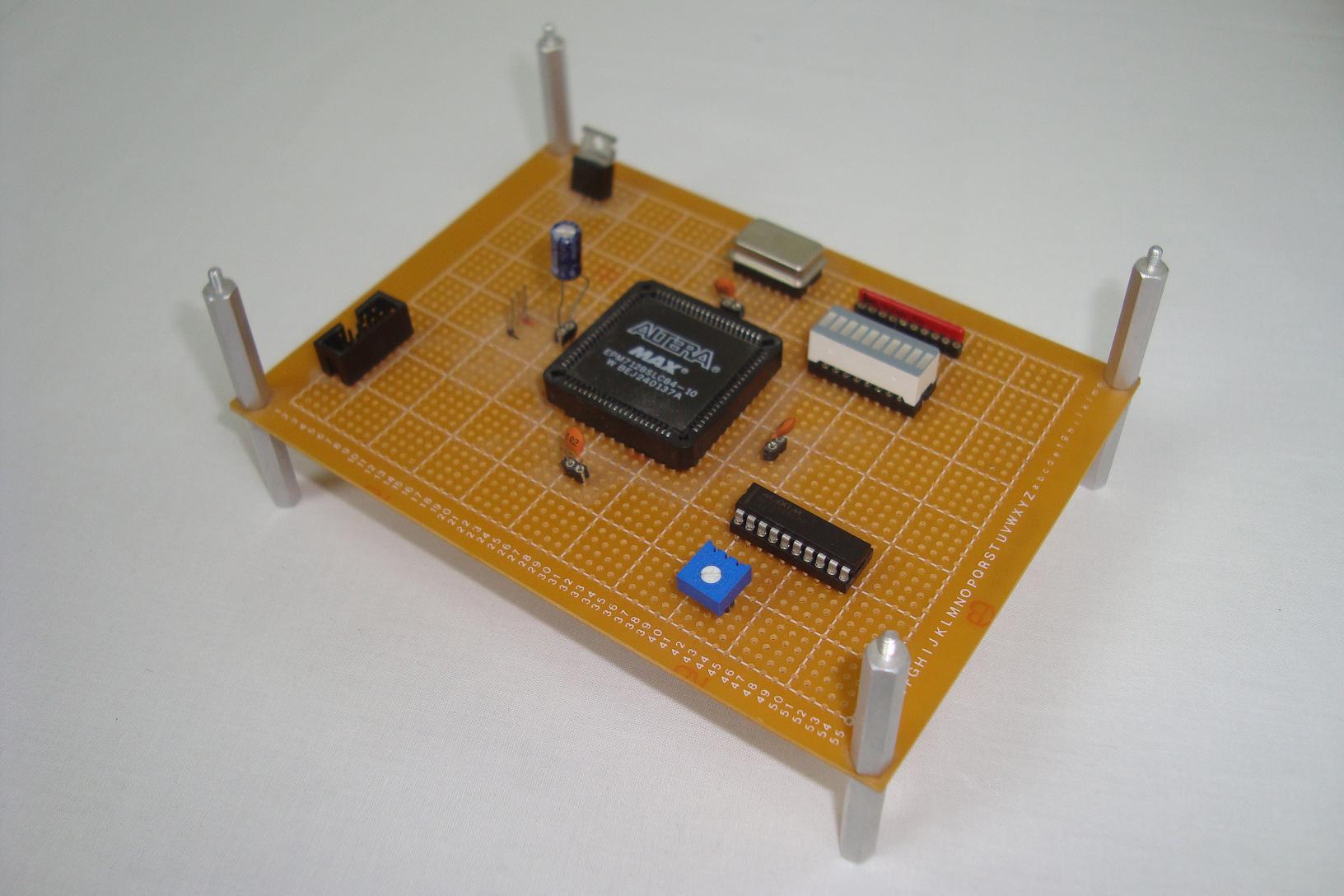

Для нового 32-х разрядного микроконтроллера было очевидно, что 1 млн вентилей может и не хватить. По этому была разработана новая плата на базе Xilinx Spartan3-5000, благодаря которой стало доступно уже 5 млн вентилей. Цена платы составила примерно 500$ и на долгое время эта плата стала основной для прототипирования новых разработок. На ее базе проверялись не только микроконтроллеры, но и различные специализированные микросхемы. Проектируемые микроконтроллер в FPGA работал уже на пониженной частоте в 20 МГц, хотя потом в кремнии работали на частотах 100 МГц и даже 150 МГц.![]()

Прототип 32-х битного микроконтроллера:

Прототип видеокарты (к сожалению в жизнь проект так и не пошел, но готовый RTL ждет своего часа):

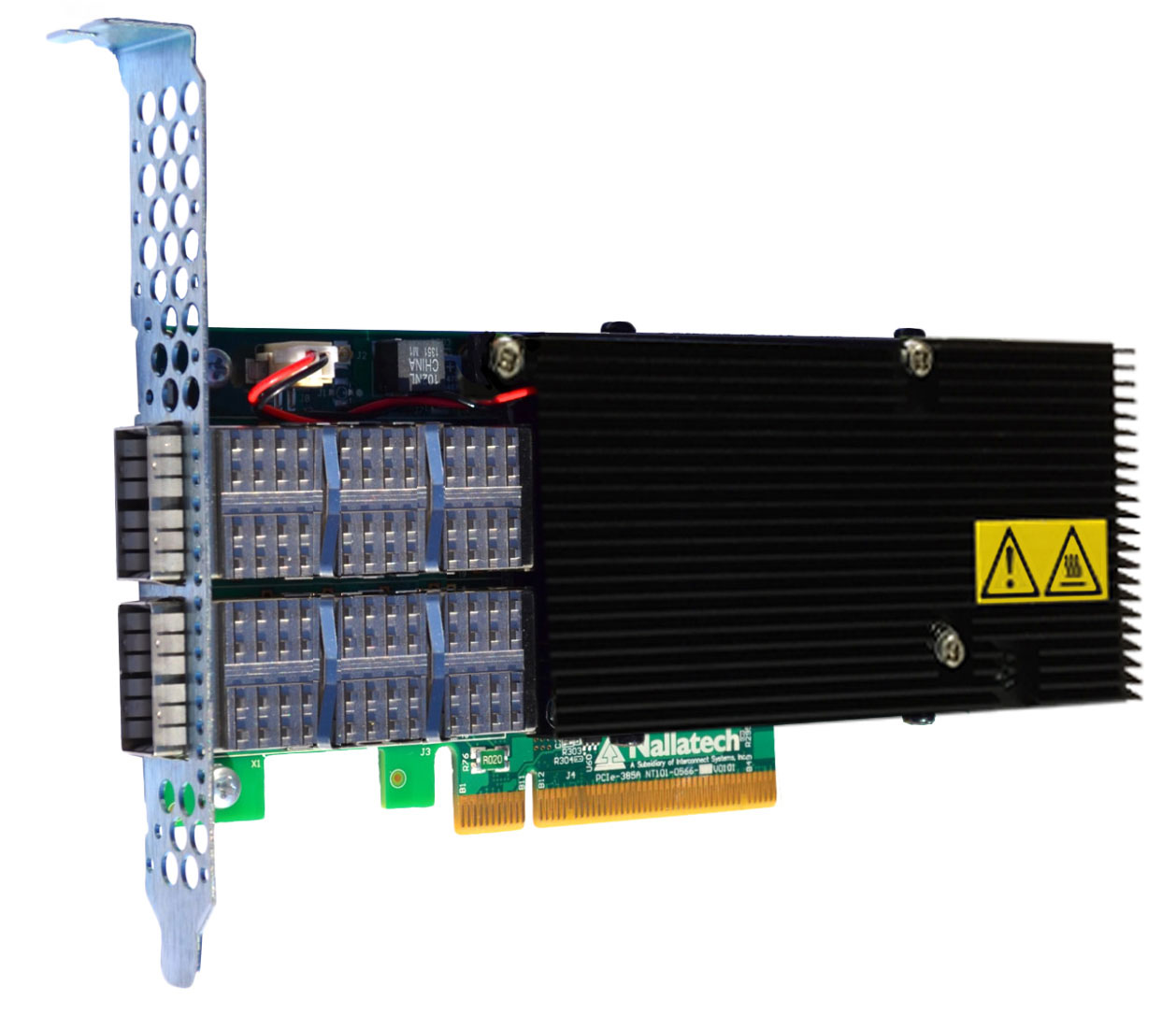

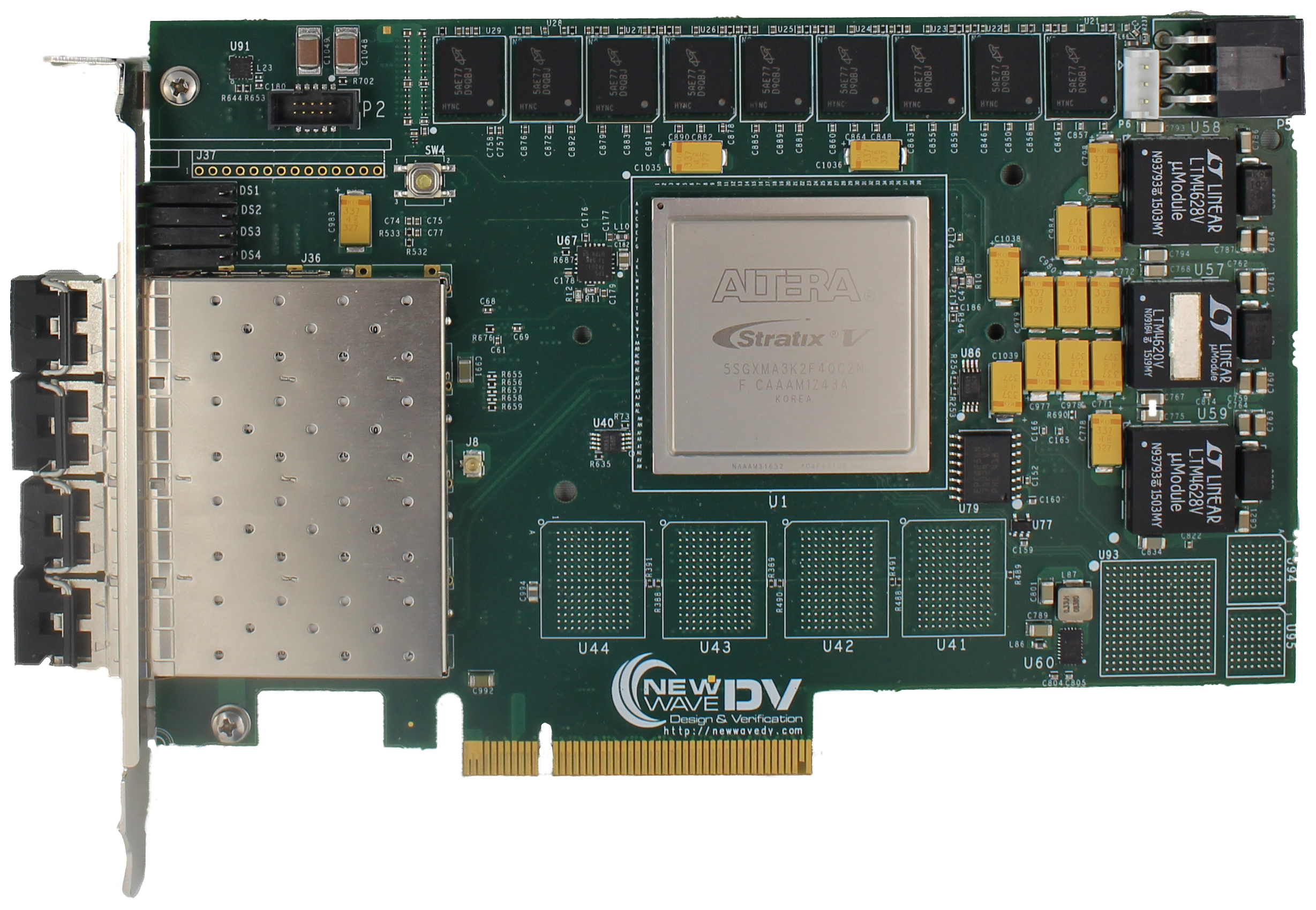

Прототип 4-х потового Ethernet коммутатор с встроенными приемопередатчиками:

2010 год

При разработке двухъядерного микроконтроллера (32-х битный RISC + 16 битное DSP ядро) мы наконец дошли до уровня, когда 5 млн было уже мало. Но реализация в FPGA различных усеченных конфигураций будущей микросхемы позволила проверить ее функционирование. Например, реализовывали два ядер (RISC+DSP) и с усеченным набором периферии или же одно ядро(RISC), но зато вся периферия.

2012 год

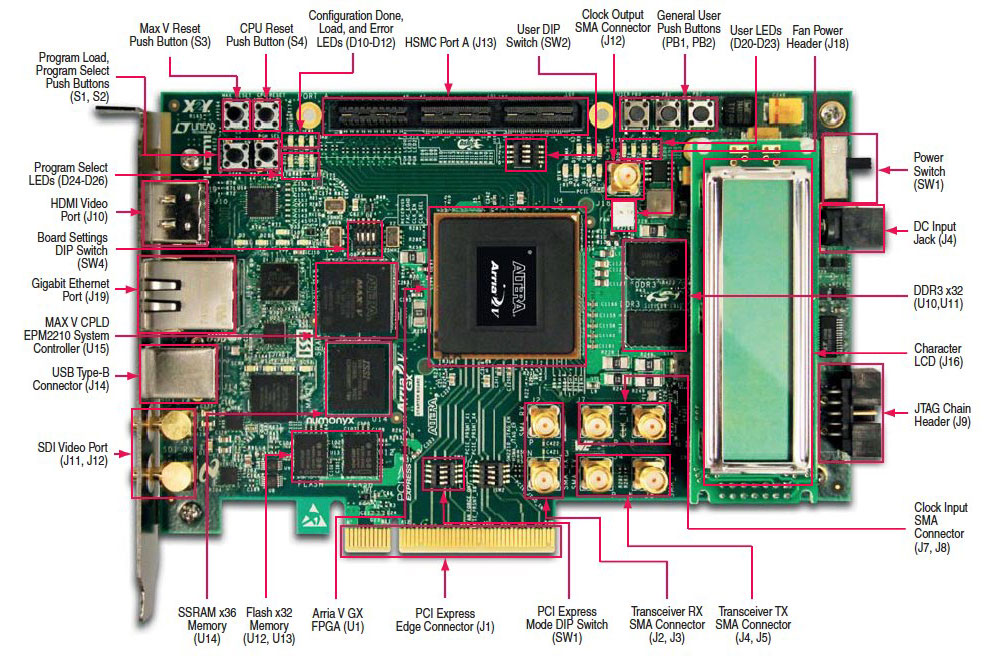

Новый проект потребовал новой платы, так как требуемый объем внутренней памяти для нового 32-х разрядного DSP ядра уже превосходил доступный объем в самой большой FPGA Spartan. Пришлось переходить на более дорогие и сложные ПЛИС. Время проекта было ограничено, и решили найти уже готовое решение. Выбор пал на плату от INREVIUM c самой большой на то время FPGA Xilinx Virtex-6 XC6VLX760.

И хотя число эквивалентный вентилей увеличилось всего до 8 млн, зато объем встроенной блочной памяти увеличился с 2 Мбит до 25 Мбит.

Выбор так же скорее всего определило то, что на сайте немецкого представительства в кэше Google сохранилась стоимость платы, и мы знали что она будет стоить 18К$ до подписания всяких NDA. А при стоимости только одной микросхемы FPGA в 15 тыс $ это снимало любые вопросы о разработке собственной платы. Серийные платы для таких больших FPGA обычно стоят либо столько же сколько и сами FPGA либо немного дороже.

Приобретение платы тоже доставило много интересных знаний, так например наш локальный дистрибьютор был убежден, что эта плата стоит 40K$ c учетом доставки, и вообще он очень рискует при 100% предоплате с нашей стороны. В конечном счете было приобретено 3 таких платы без посредников и сейчас они применяются для прототипирования наших DSP процессоров

2013 год

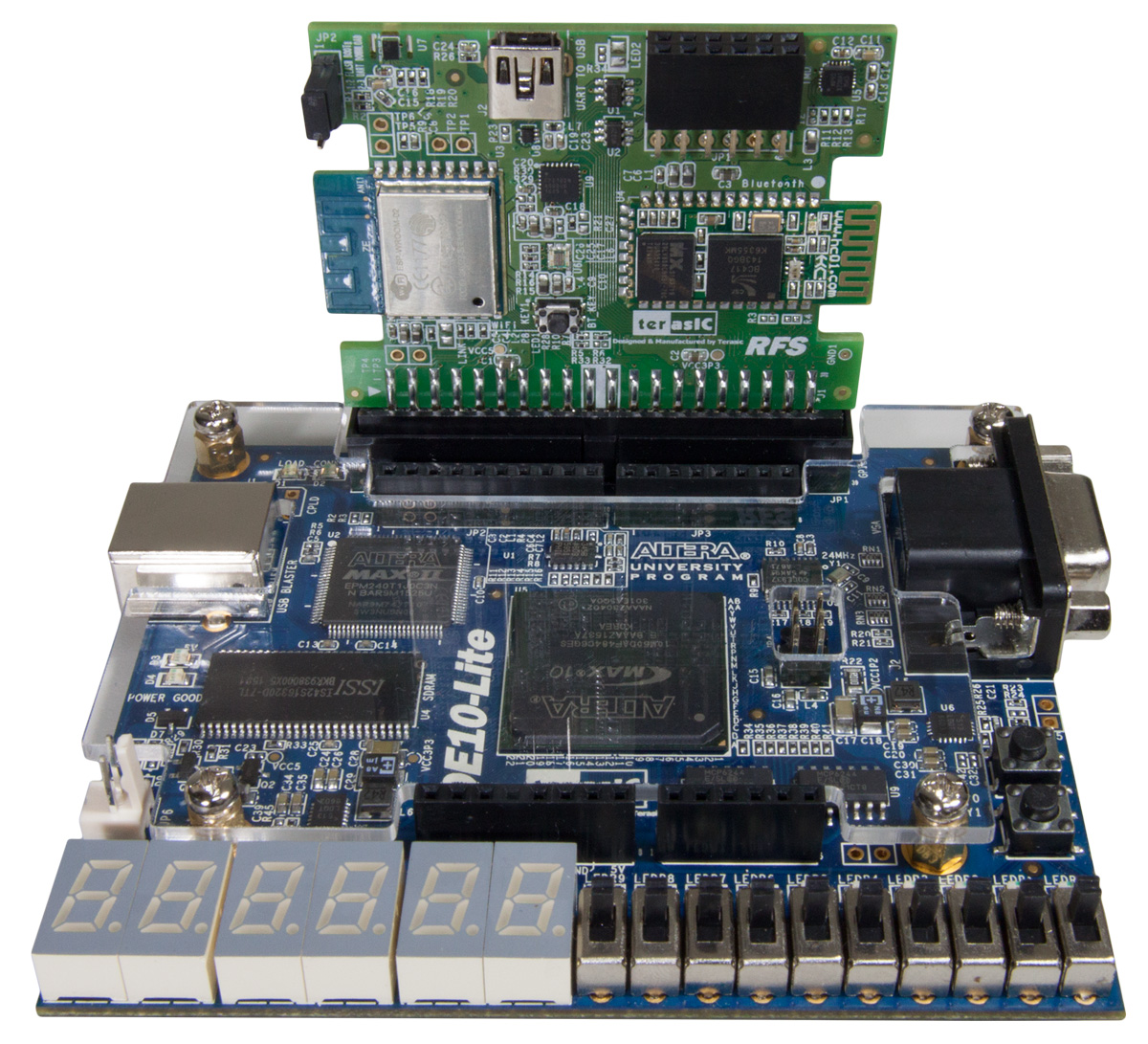

Для нового 32-х битного специализированного микроконтроллера было решено все же попробовать сделать свою плату. Во-первых, разработчики модулей на FPGA должны развиваться и не бояться применять микросхемами, которые дороже их личных автомобилей, а во-вторых у одного из дистрибьюторов завалялись на складе несколько Virtex-6 XC6VLX550Т и он предлагал их с большим дисконтом. FPGA LX550Т это на одну ступень меньше чем LX760 (примерно на 30% меньше вентилей), но зато конечная цена плат с учетом разработки составила всего около 8К$. Таких плат было собрано 6 шт. Раздавать их заказчикам мы не планировали, а организовали для разработчиков доступ к ним через интернет. В плате было реализовано много интересных решений. Например, файлы прошивок грузились на плату как на MassStorage Device в специальную SD карту, и потом уже из нее загружались в FPGA. Всего на карте может быть до 10 различных прошивок, и через специальную программу управления можно выбрать какую из них использовать в данный момент. Так же реализованы различные защиты «от дурака», что бы случайно не спалить дорогую микросхему. Все это позволяет работать с этими платами удалено, безопасно и доверять их даже студентам.

Во-первых, разработчики модулей на FPGA должны развиваться и не бояться применять микросхемами, которые дороже их личных автомобилей, а во-вторых у одного из дистрибьюторов завалялись на складе несколько Virtex-6 XC6VLX550Т и он предлагал их с большим дисконтом. FPGA LX550Т это на одну ступень меньше чем LX760 (примерно на 30% меньше вентилей), но зато конечная цена плат с учетом разработки составила всего около 8К$. Таких плат было собрано 6 шт. Раздавать их заказчикам мы не планировали, а организовали для разработчиков доступ к ним через интернет. В плате было реализовано много интересных решений. Например, файлы прошивок грузились на плату как на MassStorage Device в специальную SD карту, и потом уже из нее загружались в FPGA. Всего на карте может быть до 10 различных прошивок, и через специальную программу управления можно выбрать какую из них использовать в данный момент. Так же реализованы различные защиты «от дурака», что бы случайно не спалить дорогую микросхему. Все это позволяет работать с этими платами удалено, безопасно и доверять их даже студентам.

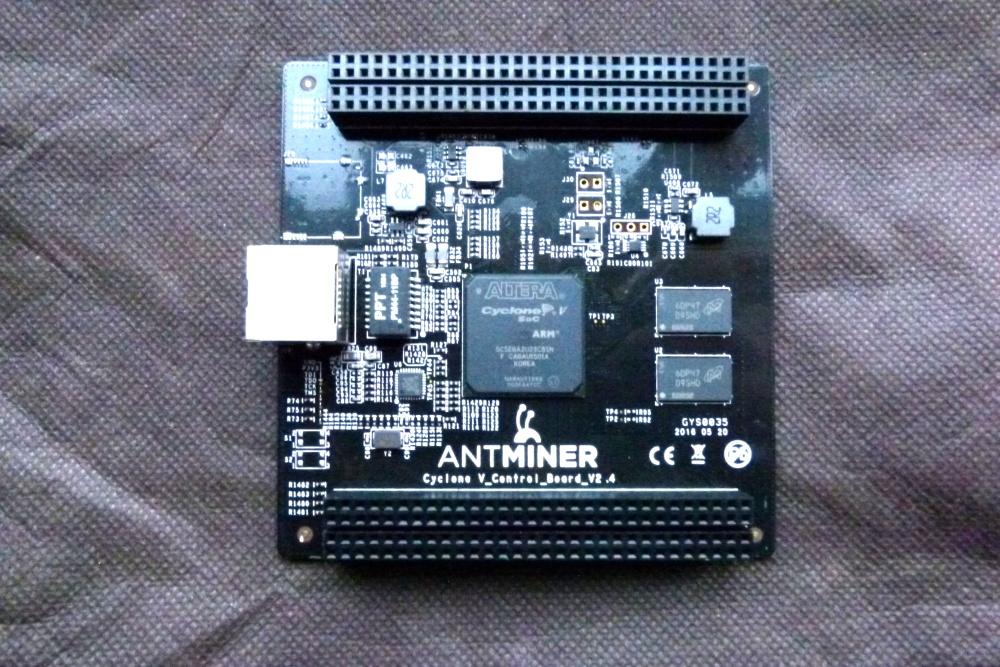

Сама плата (прототип специализированного двухъядерного 32-х битного микроконтроллера):

Прототип специализированной микросхемы для датчиков преобразования угол в код:

К сожалению в данной плате есть несколько недостатков: выбраны «дурные» разъемы для подключения дополнительных модулей, но это пол беды, забыли сделать крепежные отверстия возле разъемов, и модули держатся фактически только в разъемах. Так же что бы получить доступ к некоторым элементам управления основной платы приходится фигурно вырезать модули расширения.

Отечественный опыт

А что же другие разработчики заказных микросхем? Например МЦСТ при прототипировании СБИС 1891ВМ6Я (R-1000, четырёхъядерный процессор с 64-битной архитектурой SPARC v.9) использовала специализированную плату с 10 FPGA Altera Stratix II ( 4 х EP2S180 + 5 x EP2S130 + 1 x EP2S90). Общий объем логических вентилей системы можно оценить в 20 млн.

Сейчас одна микросхема EP2S180 стоит около 8К$.

Для прототипирования процессора Эльбрус-4C+ потребовалась уже 21 микросхема Altera Stratix IV EP4SE820 и с суммарным объемом в 100 млн. вентилей (хотя сам МЦСТ приводит цифру в 750 млн) и стоимостью около 200К$. При этом рабочая частота прототипа 9 МГц.

Зарубежный опыт

Сейчас специализированные решения для FPGA прототипирования предлагают компании специализирующиеся на разработке средств САПР для микроэлектроники, хотя пригодные для прототипирования модули можно найти и у других компаний. FPGA прототипы есть у Intel и IBM, но их характеристики не афишируются, и становятся известны широкому кругу, только тогда, когда прототип уже моральна устарел.

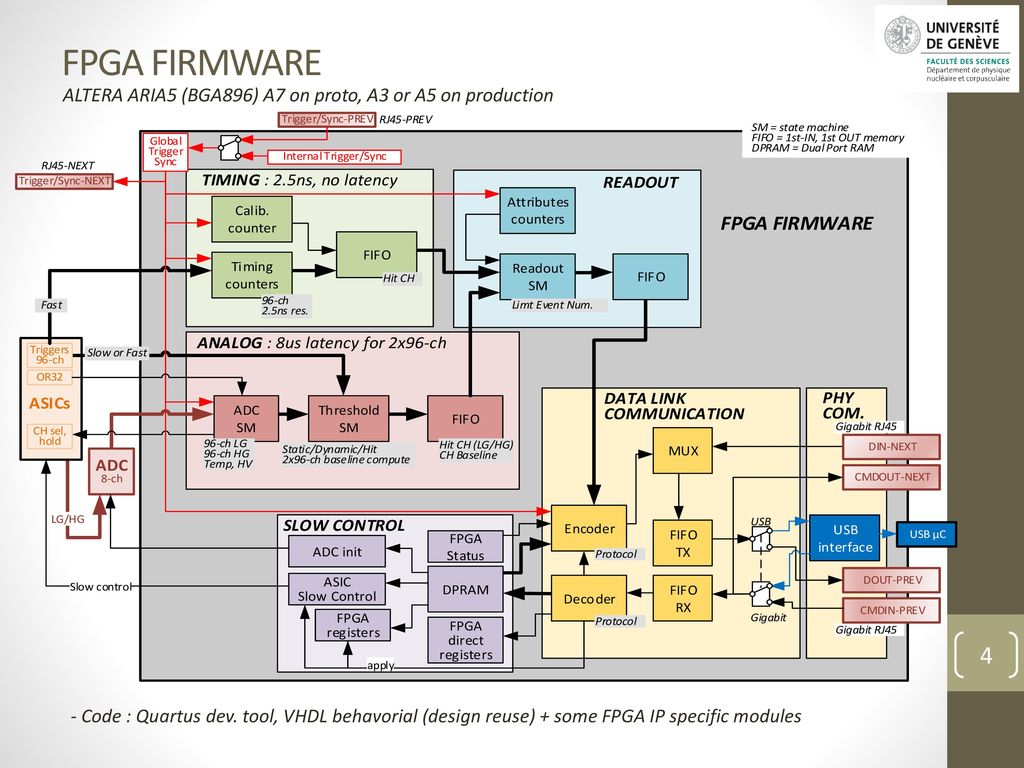

Cadence предлагает специальную Rapid Prototyping Platform построенную на базе FPGA Altera Stratix-4 EP4SE820. В минимальной конфигурации платформа состоит из двух (c суммарным объемом в 10 млн вентилей), в максимальной из шести FPGA (c объемом до 30 млн вентилей). Цена одной микросхемы EP4SE820 сегодня ~10К$.

Цена одной микросхемы EP4SE820 сегодня ~10К$.

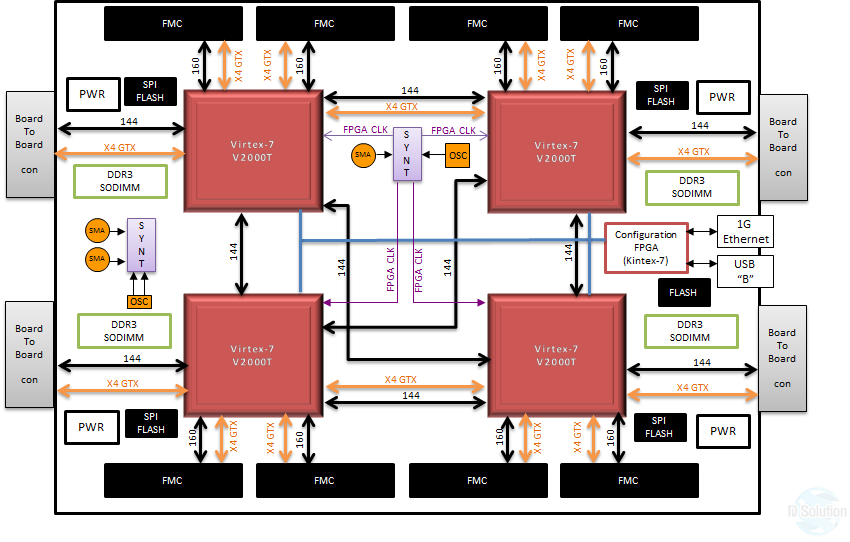

Новая система от Cadence носит название Protium и стоится на базе Xilinx Virtex-7 XC7V2000Т и позволяет реализовать от 25 млн на двух FPGA до 100 млн вентилей на восьми. Стоимость одной микросхемы XC7V2000Т сейчас около 20К$. Т.е. в полной комплектации Protium будет стоить не менее 160К$.

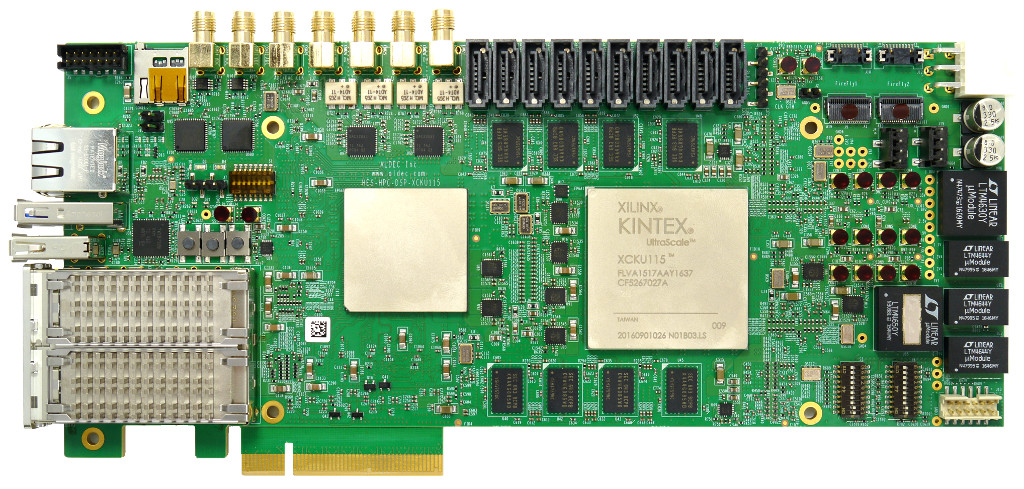

Компания Aldec помимо средств разработки так же предлагает платформу для FPGA протоипирования HES-7.

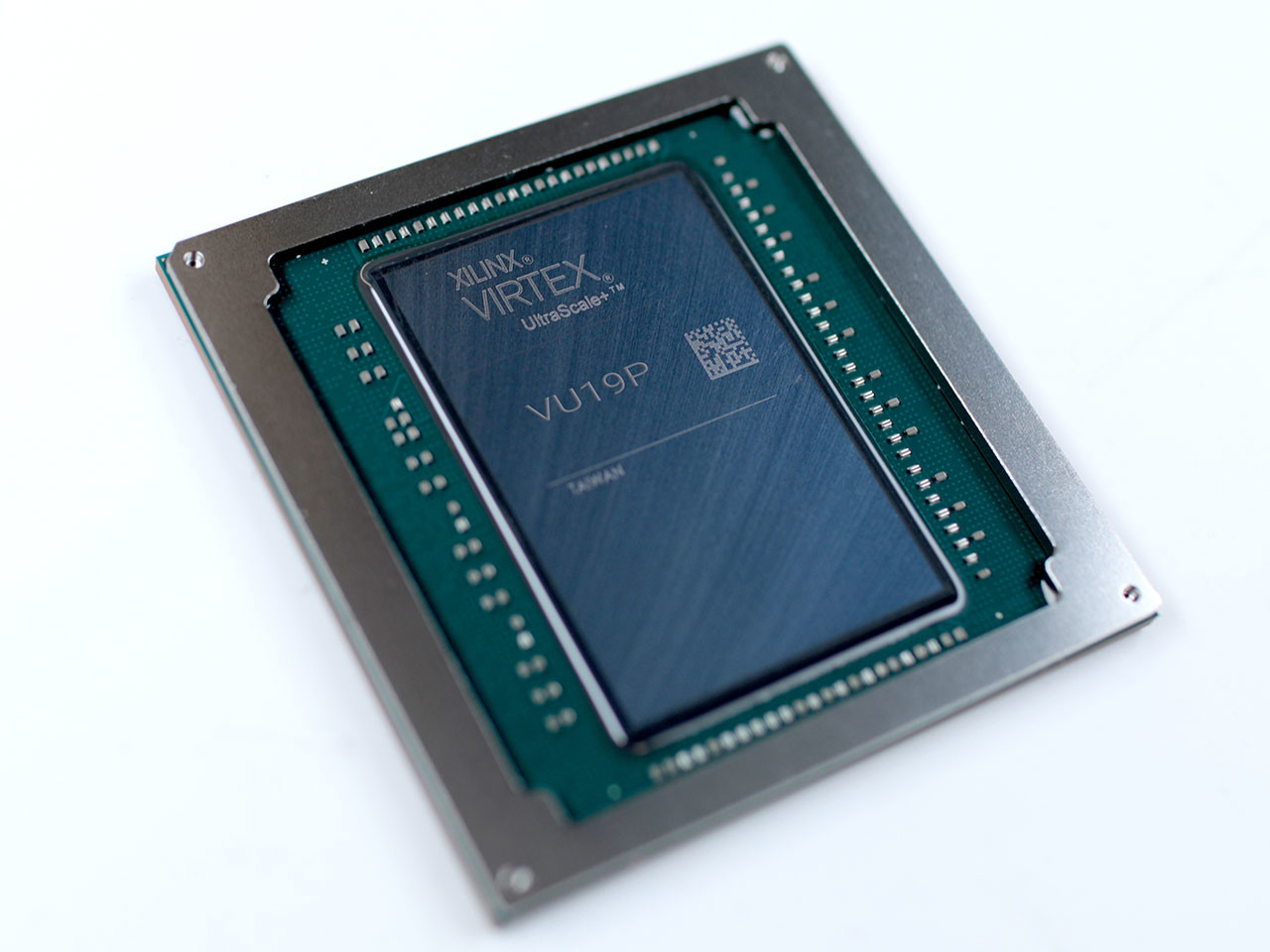

На одной плате расположено до шесть FPGA Xilinx Virtex-7 XC7V2000Т или UltraSacle XCVU440. В случае реализации модуля на базе FPGA UltraSacle XCVU440 суммарное число вентилей достигает 158 млн. С помощью дополнительной платы можно собрать в единый модуль 24 микросхемы FPGA и получить 633 млн вентилей. Стоимость одной микросхемы XCVU440 сейчас 49К$. А максимальная суммарная стоимость всех FPGA переваливает за 1М$.

Synopsys имеет наверное наибольший опыт в разработке платформ для FPGA прототипирвоания. Ранние их модели строились на базе FPGA Virtex-6 (HAPS-60), затем Virtex-7 (HAPS-70). Последняя их разработка HAPS-80 в одном модуле содержит от одной до четырех FPGA Xilinx UltraScale XCVU440.

Последняя их разработка HAPS-80 в одном модуле содержит от одной до четырех FPGA Xilinx UltraScale XCVU440.

Готовые модули можно объединять в единую стойку. И в этом случае суммарный объем составляет рекордные 1,6 млрд вентилей.

При использовании одной FPGA максимальная частота до 300 МГц, при использовании соседних в одном модуле до 100 МГц, при использовании нескольких модулей частота снижается до 30 МГц.

Таким образом, имея примерно 3,5М$ на приобретение FPGA вы сможете собрать платформу пригодную для прототипирования Intel Xeon E7. Ну или подождать 20 лет, когда FPGA такого объема подешевеют до пары сотен долларов.

Какая самая большая разница между ASIC и FPGA

источник:http://m.elecfans.com/article/635174.html

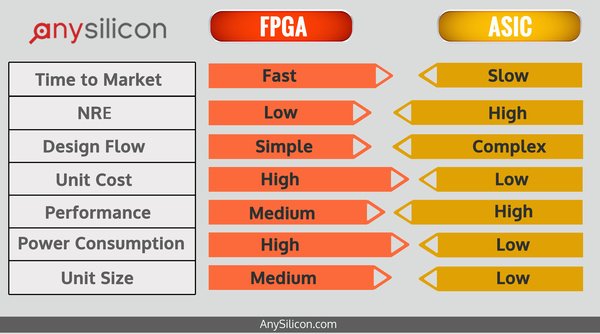

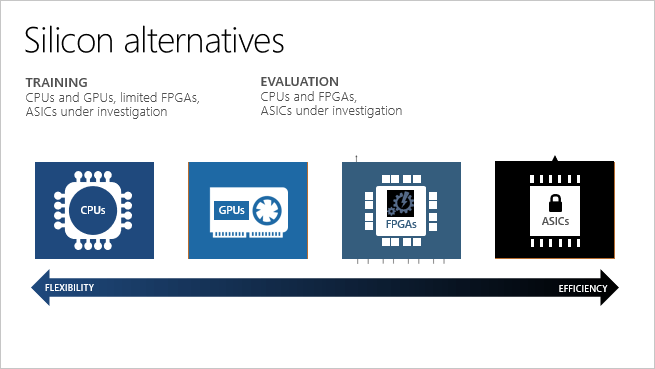

Специфичные для приложений интегральные схемы (ASIC) используют фиксированный фиксированный режим, в то время как программируемые вентильные матрицы (FPGA) используют настраиваемый метод микросхем, и они сильно различаются. Программируемые устройства являются новой силой в настоящее время, и гибридные технологии также будут играть роль в будущем.

Программируемые устройства являются новой силой в настоящее время, и гибридные технологии также будут играть роль в будущем.

Как и другие технологии, устаревшие отчеты по технологии ASIC являются незрелыми. Число новых продуктов ASIC, возможно, значительно сократилось, но их продажи все еще довольно высоки, особенно в Азиатско-Тихоокеанском регионе. Кроме того, использование гибридных методов, таких как структурированные микросхемы ASIC, также придает новую жизнеспособность технологии. В то же время FPGA (и другие программируемые логические устройства) также играют роль, завоевывая важный массовый рынок и продолжая развиваться из недорогих приложений.

У каждой технологии есть свои сторонники. Вообще говоря, ASIC используется для крупномасштабных проектов, а для небольших проектов, которые должны быть быстро выведены на рынок и поддерживать удаленные обновления, FPGA являются более подходящими. Поставщики ASIC и FPGA не могут договориться о преимуществах и недостатках этих двух технологий и придерживаются разных взглядов на подходящие области применения. Вышеуказанные технологии и их производные технологии, вероятно, будут существовать еще долго в будущем.

Вышеуказанные технологии и их производные технологии, вероятно, будут существовать еще долго в будущем.

Старший директор Altera Corp. по высокопроизводительной ПЛИС Дэвид Гринфилд отметил, что основным преимуществом технологии ПЛИС остается короткое время выхода на рынок. Он сказал: «В нынешних недавно добавленных схемах проектирования выбор ПЛИС, как правило, превышает ASIC. Технология ASIC имеет свою ценность, ее производительность, плотность и емкость устройства очень хороши, но с развитием ПЛИС и развитием ASIC Рост стоимости приведет к сокращению доли рынка ASIC. «Именно развитие FPGA в производительности, плотности и стоимости производства играет роль после вышеупомянутой тенденции.

Гринфилд отметил, что высокая производительность раньше была преимуществом ASIC перед FPGA, когда FPGA уступала в производительности и функциональности. Поскольку процесс производства микросхем эволюционировал от 180 нм до 130 нм или даже 90 нм, описанная выше ситуация сильно изменилась. Теперь производительность FPGA может удовлетворить потребности большинства приложений (за исключением самых требовательных приложений), тогда как уровень плотности достигает логического дизайна. 80%. Он пояснил: «Некоторые разработчики систем также признают, что область рынка ASIC — это продукты с очень высокой производительностью / плотностью, и эта область рынка очень рискованна. NRE (неповторяющееся проектирование) и затраты на разработку для этого оборудования С точки зрения самого высокого «.

Теперь производительность FPGA может удовлетворить потребности большинства приложений (за исключением самых требовательных приложений), тогда как уровень плотности достигает логического дизайна. 80%. Он пояснил: «Некоторые разработчики систем также признают, что область рынка ASIC — это продукты с очень высокой производительностью / плотностью, и эта область рынка очень рискованна. NRE (неповторяющееся проектирование) и затраты на разработку для этого оборудования С точки зрения самого высокого «.

Altera указала, что более ранние ПЛИС использовались только для создания прототипов или приложений с малой емкостью / низкой плотностью, а теперь эта технология широко используется в продуктах бытовой электроники, а также в приложениях с высокой плотностью. Гринфилд отметил, что FPGA с самой высокой плотностью (90 нм) по-прежнему значительно выше в цене за единицу, чем ASIC. Он сказал: «Тем не менее, даже для приложений с высокой плотностью, при рассмотрении факторов стоимости разработки и NRE, результат все еще склонен к технологии FPGA».

Работа ASIC в Texas Instruments (TI) в основном основана на модульном методе, обслуживающем ограниченное число крупных клиентов. Среднее число шлюзов в этих устройствах ASIC обычно в пять раз больше, чем у отраслевых стандартных ASIC, и в основном используется в очень сложных и высокопроизводительных приложениях. Эти приложения требуют дифференцированных коммерческих сетевых и телекоммуникационных технологий.

Джон ДиФилиппо, дизайнер кремниевых технологий в подразделении коммуникационной инфраструктуры ASIC компании TI, отметил: «Разработка ASIC единичным способом требует более высоких начальных инвестиций. Однако при высокой производительности рентабельность инвестиций будет значительно улучшена из-за меньшего количества микросхем и более низкой стоимости единицы. Когда цена за единицу готового продукта не важна, или когда время выхода на рынок невелико, или когда первоначальные инвестиции малы, ПЛИС является лучшим выбором ».

ДиФилиппо считает, что клиенты TI требуют хорошего соотношения цена-качество, которого трудно достичь ПЛИС и структурированным ASIC. FPGA и структурированная ASIC больше подходят для широкого среднего рынка. Он сказал: «ПЛИС и структурированные интегральные микросхемы подходят для небольших по объему приложений с коротким сроком службы. Клиенты готовы пожертвовать функциями и производительностью продукта, но им все же необходимо достичь системных целей».

FPGA и структурированная ASIC больше подходят для широкого среднего рынка. Он сказал: «ПЛИС и структурированные интегральные микросхемы подходят для небольших по объему приложений с коротким сроком службы. Клиенты готовы пожертвовать функциями и производительностью продукта, но им все же необходимо достичь системных целей».

Тем не менее, TI согласен с обеими конкурирующими технологиями. Компания TI представила новые функции для устройств ASIC на основе ячеек, что позволяет ей обеспечивать гибкость, подобную матрице шлюзов, сокращать время цикла и снижать стоимость при изменении требований к устройству. Компания TI также разработала «платформенные» продукты ASIC, которые можно использовать в нескольких продуктовых линейках клиентов, и отметила, что это может снизить стоимость разработки единичных систем.

TI считает, что унитарный метод ASIC наиболее подходит для следующих ситуаций:

■ количество дверей и складских помещений превышает 10 миллионов;

■ Большое количество гигабитных соединений;

■ При минимальном энергопотреблении основная тактовая частота выше 300 МГц;

■ Чувствительные к стоимости приложения.

Возможные альтернативы

Xilinx отметил, что дебаты о том, может ли FPGA стать жизнеспособной альтернативой ASIC и связанным стандартным устройствам, продолжались почти десятилетие. Эрих Геттинг, вице-президент отдела передовых продуктов Xilinx, отметил, что, хотя FPGA добились значительного прогресса со временем, до недавнего времени разработчики должны использовать большие и дорогие устройства для достижения высокой производительности, а обработка DSP и RISC необходима для конкретных приложений. Или высокоскоростное последовательное соединение.

Теперь Xilinx предоставляет новую «платформу оптимизации доменов FPGA» (Virtex-4), которая может увеличивать или уменьшать конструкцию чипа в соответствии с функциональными требованиями и целями приложения в соответствии с архитектурой ASMBL (модуль). Геттинг отметил: «ASMBL — это модульная структура для подсистем кремниевой технологии, которая предоставляет новый метод разработки FPGA для быстрого и дешевого развертывания платформ для различных областей применения». Например, для разработки могут потребоваться высокоскоростные функции DSP, но не Требуется продвинутая логика. Благодаря архитектуре ASMBL Virtex-4 позволяет пользователям выбирать подходящую комбинацию логики, DSP, памяти и других функций (сгруппированных по столбцам) в соответствии с конкретной схемой. Было отмечено, что архитектура типа столбца может обеспечивать до 17 видов опций устройства и может предоставлять больше функций в «настройке цены».

Например, для разработки могут потребоваться высокоскоростные функции DSP, но не Требуется продвинутая логика. Благодаря архитектуре ASMBL Virtex-4 позволяет пользователям выбирать подходящую комбинацию логики, DSP, памяти и других функций (сгруппированных по столбцам) в соответствии с конкретной схемой. Было отмечено, что архитектура типа столбца может обеспечивать до 17 видов опций устройства и может предоставлять больше функций в «настройке цены».

Xilinx отметил, что, поскольку затраты на NRE практически отсутствуют (как правило, распределяются между поставщиками FPGA), FPGA, как правило, имеют ценовое преимущество. Геттинг отметил: «Затраты на разработку ASIC быстро и быстро росли, и с ростом функциональности платформ FPGA это нарушило баланс конкурентного преимущества по отношению к FPGA. Помимо широкого использования в области аналогового / смешанного сигнала, ASIC сложно обеспечить по сравнению с FPGA. Другие существенные функциональные преимущества. «FPGA также могут экономить затраты в других отношениях, и их можно исправить с помощью загрузки программного обеспечения, а также удобно отлаживать производительность системы при добавлении новых функций.

Рисунок 1: На рисунке показана скорость роста FPGA (тип программируемого логического устройства) и SIC, опубликованных Ассоциацией полупроводников на мировом рынке.

GE Fanuc Automation считает, что «настоящие преимущества» ПЛИС двояки: во-первых, их можно быстро разработать с использованием надежных стандартных компонентов, и их можно легко модифицировать для добавления новых функций, во-вторых, они могут быть разработаны или в течение жизненного цикла продукта. Исправление ошибок. Старший инженер GE Fanuc Ричард Рид отметил, что, в отличие от ASIC, FPGA как встроенный стандарт также имеет больше функций, таких как тестируемость или интерфейс JTAG, которые могут сэкономить время проектирования и затраты.

ПЛИС ускорила внедрение продуктов. Рид отметил: «Большое количество стандартных компонентов делает цену FPGA более конкурентоспособной, чем ASIC. Для приложений с длительным жизненным циклом и большим выходом иногда бывает более целесообразно преобразовать конструкцию в специализированный чип ASIC».

Что касается преимуществ ASIC, то Рид отметил, что ASIC могут работать сразу после включения питания, что касается размера логики устройства, вариантов пакета больше, и некоторые аналоговые логики также могут быть включены. Напротив, FPGA требуют времени для загрузки конфигурации и ввода в память, поэтому они не могут работать сразу. Кроме того, упаковка FPGA является более сложной.

Факторы стоимости / риска

Nallatech является разработчиком вычислительных систем, программного и аппаратного обеспечения для ПЛИС. Компания признает, что ASIC достигли «высокого уровня производительности» с точки зрения конкретных типов функций и специализированных приложений, для которых они предназначены. Тем не менее, инженер по системным приложениям Nallatech Крейг Сандерсон отметил, что если ASIC используются для реализации высокопроизводительных функций обработки (таких как промышленное моделирование, моделирование или создание изображений), это приведет к «коммерческому воздействию».

Рисунок 2: ПЛИС успешно применена к промышленным продуктам, таким как CompactRIO от NI

Чип FPGA, встроенный в реконфигурируемую систему сбора и управления, играет важную роль.

В контроллере GE FANUC PA CSystems RX3i также используется технология FPGA.

Вышеупомянутые «высокопроизводительные» приложения обычно имеют малый и средний масштаб. Хотя Сандерсон не дал критической точки для эффективности затрат приложений, использующих ASIC, он отметил, что с точки зрения затрат / рисков ASIC не осуществимы для относительно небольших приложений. «Он добавил, что независимо от масштаба,« производители ПЛИС обычно поощряют использование ПЛИС, а не ASIC. «

Nallatech также считает, что FPGA позволяет избежать более высоких затрат на NRE и имеет другие преимущества. Возможность перепрограммирования ПЛИС обеспечивает более гибкий путь разработки, снижая риски и затраты. Напротив, разработка ASIC должна быть «впервые определенно правильной». Возможность перепрограммирования FPGA позволяет разработчикам использовать пакеты обновления программного обеспечения для модификации чипа, запуская программы на чипе вместо замены чипа. ПЛИС даже можно обновить удаленно через Интернет. Контроль устаревания относится к существующему дизайну приложений FPGA как доступному ресурсу для перекомпиляции устройств нового поколения.

ПЛИС даже можно обновить удаленно через Интернет. Контроль устаревания относится к существующему дизайну приложений FPGA как доступному ресурсу для перекомпиляции устройств нового поколения.

Для многих приложений производители ПЛИС заявили, что производительность сопоставима с ASIC. Сандерсон отметил: «Что касается высокопроизводительных приложений, ПЛИС предоставляют достаточные ресурсы для выполнения функций, эквивалентных технологии ASIC, и в то же время гораздо более высокую производительность, чем стандартные процессоры».

Поскольку FPGA может быть перепрограммирована, приложение может быть отлажено и протестировано на реальном оборудовании. Сандерсон добавил: «Что касается ASIC, все проверки должны быть выполнены до начала физической реализации аппаратной стадии ASIC. Если уже слишком поздно обнаруживать проблемы на аппаратной стадии».

Гриша Ретер (Gricha Raether) — менеджер по промышленному контролю и распределенному вводу-выводу компании National Instruments (NI). Он отметил, что ASIC и FPGA раньше использовались для крупномасштабных приложений, таких как машиностроение и интеграция OEM-типа, что помогает выделять традиционно высокие показатели. Затраты на разработку. Причиной высокой стоимости является то, что у него длинный цикл разработки для вышеупомянутых устройств, и разработчикам необходимо овладеть многими профессиональными знаниями об инструментах разработки, особенно проектных работах и этапах изготовления ASIC.

Он отметил, что ASIC и FPGA раньше использовались для крупномасштабных приложений, таких как машиностроение и интеграция OEM-типа, что помогает выделять традиционно высокие показатели. Затраты на разработку. Причиной высокой стоимости является то, что у него длинный цикл разработки для вышеупомянутых устройств, и разработчикам необходимо овладеть многими профессиональными знаниями об инструментах разработки, особенно проектных работах и этапах изготовления ASIC.

Продукты FPGA хорошо разработаны и могут быть запрограммированы напрямую. Он отметил, что в этом отношении ПЛИС будет постепенно заменять фактическую интегральную схему. Поскольку FPGA имеют настраиваемую гибкость, поставщики могут брать больше. Разработка IC-пакетов и печатных плат принесет больше затрат, которые одинаковы для обеих технологий, но это особенно верно для ASIC.

Промышленный жизненный цикл

Ретер считает, что FPGA также полезна для промышленных продуктов с более длинным жизненным циклом. Это главным образом потому, что технология может быть легко перепрограммирована в соответствии с новой версией и может быть перепрограммирована на месте. Он сказал: «Разработчики, использующие технологию FPGA, должны учитывать расширение и модификацию, которые могут потребоваться, и должны заранее подготовиться к выбору количества вентилей FPGA». Для этого требуется количество массивов вентилей и программирование микросхем, необходимых для реализации этой функции. Достигается тонкий баланс между достигнутой производительностью в дополнение к требуемому «пространству для хранения».

Это главным образом потому, что технология может быть легко перепрограммирована в соответствии с новой версией и может быть перепрограммирована на месте. Он сказал: «Разработчики, использующие технологию FPGA, должны учитывать расширение и модификацию, которые могут потребоваться, и должны заранее подготовиться к выбору количества вентилей FPGA». Для этого требуется количество массивов вентилей и программирование микросхем, необходимых для реализации этой функции. Достигается тонкий баланс между достигнутой производительностью в дополнение к требуемому «пространству для хранения».

Altera также считает, что FPGA также «очень выгодны» для промышленных продуктов с более длинным жизненным циклом, хотя продажи таких продуктов со временем будут снижаться. Гринфилд отметил: «Технология FPGA не требует минимального количества резервирований и имеет более длительный срок службы, что является важной причиной ее уникальности. Многие промышленные клиенты, которые проектировали продукты ASIC в течение пяти лет, теперь используют FPGA вместо ASIC». Есть много причин. Например, ASIC требует минимального количества заказа, что является очень негибким, технология процесса ASIC устарела или должна быть преобразована в упаковку чипов без свинца.

Есть много причин. Например, ASIC требует минимального количества заказа, что является очень негибким, технология процесса ASIC устарела или должна быть преобразована в упаковку чипов без свинца.

Технологические процессы постепенно устаревают — проблема, с которой сталкиваются производители микросхем. Гринфилд отметил: «Эта проблема особенно серьезна для компаний ASIC, потому что их клиентская база очень ограничена, и, вероятно, будет трудно уйти от трудностей».

Роль программных инструментов

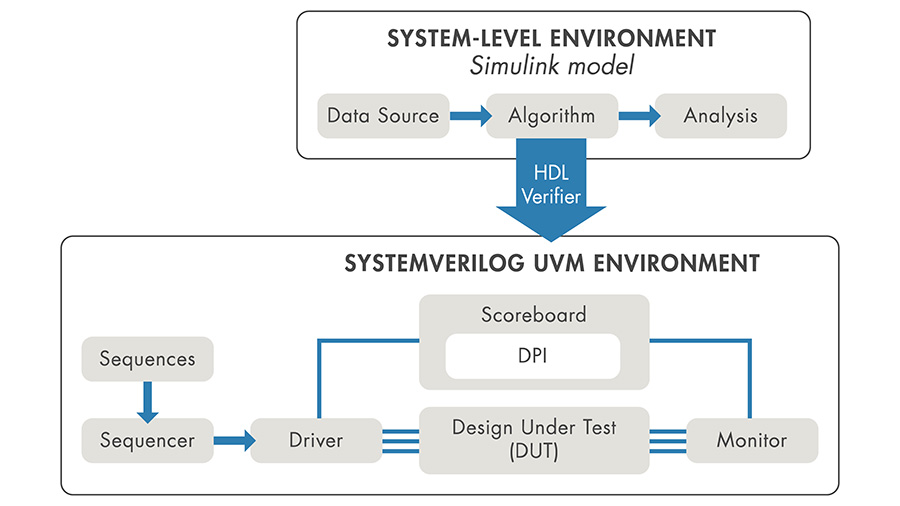

Разработка решений FPGA довольно сложна и требует соответствующих программных средств. Сандерсон из Nallatech отметил, что средства проектирования FPGA постоянно совершенствуются, особенно те, которые используют языки высокого уровня или интерфейсы для разработки приложений, такие как MatLab / Simulink, предоставляемые Mathworks.

Он сказал, что языки высокого уровня особенно важны для компаний ПЛИС, потому что этот язык может упаковать необходимые прикладные функции в одно или несколько устройств ПЛИС. Сандерсон отметил, что ранее эта функция должна быть реализована на одном или нескольких DSP или микропроцессорах, и для достижения соединения необходимо добавить некоторые ASIC с фиксированной функцией.

Сандерсон отметил, что ранее эта функция должна быть реализована на одном или нескольких DSP или микропроцессорах, и для достижения соединения необходимо добавить некоторые ASIC с фиксированной функцией.

Подобные и разные кремниевые технологии

ASIC и FPGA являются интегральными схемами (IC), но они отличаются друг от друга. Как следует из названия, специализированная интегральная схема (ASIC) — это микросхема с твердым проводным соединением, которая специально удовлетворяет специфическим потребностям определенного электронного продукта или серии продуктов и используется в различных потребительских электронных продуктах и промышленных продуктах.

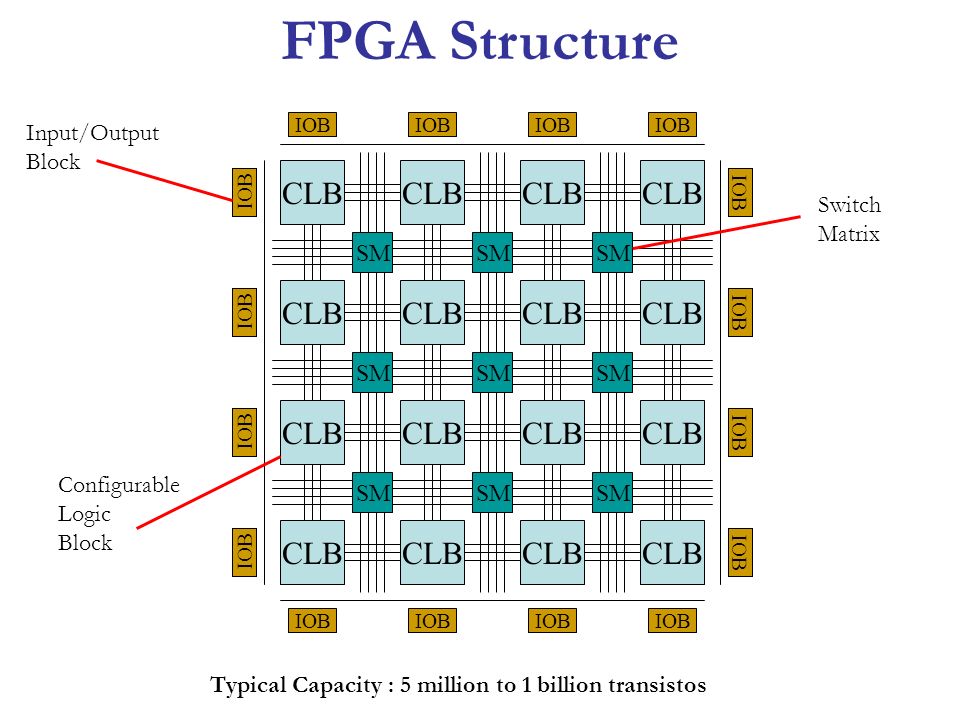

Полевая программируемая матрица логических элементов (FPGA) — это новая технология ИС, включающая в себя десятки тысяч логических ячеек, соединенных программируемыми переключателями, через логическое соединение ячеек для удовлетворения различных требований к конструкции. В дополнение к логическому блоку другими программируемыми компонентами FPGA являются блок ввода-вывода (используемый в качестве интерфейса для внутренних одиночных линий и внешних выводов микросхемы) и интерфейс межсоединения (маршрутизация сигналов ввода-вывода других компонентов в соответствующую сеть). Функция перепрограммирования — самое большое преимущество такого рода устройств.

Функция перепрограммирования — самое большое преимущество такого рода устройств.

Структурированная ASIC является средним звеном вышеупомянутого метода и использует металлический базовый слой для предварительного изготовления элементов дизайна (логическое устройство, память, ввод / вывод и т. Д.), Общих для многих приложений. Данные для конкретных применений могут быть добавлены к последним нескольким металлическим слоям, что значительно уменьшает количество слоев маски и снижает стоимость разработки до исследования.

Одна из сложностей проектирования, с которой сталкиваются дизайнеры, заключается в реализации связи между несколькими функциональными блоками в одной FPGA. Считается, что инструмент DimeTalk компании Nallatech (в настоящее время применим только к оборудованию Nallatech) решает проблему разработки систем связи FPGA.

Каждая технология чипа требует инструментов дизайна. Xilinx отметил, что из-за особенностей процесса проектирования ПЛИС пользователям ПЛИС не нужно учитывать производственный выход и субмикронные проблемы. Кроме того, ПЛИС обладают также преимуществами простоты использования, низкой стоимости и короткого времени выхода на рынок. Геттинг добавил: «Как стандартный продукт, FPGA были полностью протестированы, когда они были запущены, и могут нормально функционировать, потому что поставщики FPGA решили проблемы физического проектирования, проверки и определения характеристик». Xilinx — это логика, DSP и встроенные устройства обработки. Предоставляют интегрированные инструменты проектирования и отладки, а также предоставляют интерфейсы для сторонних инструментов.

Кроме того, ПЛИС обладают также преимуществами простоты использования, низкой стоимости и короткого времени выхода на рынок. Геттинг добавил: «Как стандартный продукт, FPGA были полностью протестированы, когда они были запущены, и могут нормально функционировать, потому что поставщики FPGA решили проблемы физического проектирования, проверки и определения характеристик». Xilinx — это логика, DSP и встроенные устройства обработки. Предоставляют интегрированные инструменты проектирования и отладки, а также предоставляют интерфейсы для сторонних инструментов.

По словам разных поставщиков, программное обеспечение для программирования ПЛИС отличается по содержанию и дополнительным функциям (таким как инструменты компиляции и редактирования). Н.И.Ретер подчеркнул, что для умения использовать вышеуказанные инструменты требуются годы опыта и обучения. Он сказал: «Некоторые более продвинутые инструменты постепенно выходят на рынок, но необходимо понимать внутренний механизм FPGA, чтобы использовать эти инструменты». VHDL (Very [High Speed] Language Description Language) является наиболее часто используемым языком разработки. Ретер сказал, что программное обеспечение NI LabView может полностью абстрагировать внутренний механизм работы устройства, и в настоящее время это единственное программное обеспечение, которое реализует эту функцию. Программное обеспечение может программировать ПЛИС в программируемом контроллере автоматизации через графическую среду разработки.

VHDL (Very [High Speed] Language Description Language) является наиболее часто используемым языком разработки. Ретер сказал, что программное обеспечение NI LabView может полностью абстрагировать внутренний механизм работы устройства, и в настоящее время это единственное программное обеспечение, которое реализует эту функцию. Программное обеспечение может программировать ПЛИС в программируемом контроллере автоматизации через графическую среду разработки.

Испытайте гибридные решения

ПЛИС также сталкивается с проблемами. Xilinx отметил, что статическое потребление энергии и ограничения по размеру чипов высокой плотности являются проблемами FPGA, потому что программируемые чипы требуют больше транзисторов для выполнения логических функций. Хотя процессы FPGA эволюционировали в более новые, более мелкие технологии, инновации на уровне процессов, на уровне цепей и на уровне архитектуры, по-видимому, все больше ограничиваются проблемами энергопотребления. Геттинг отметил, что, например, Xilinx снизил энергопотребление своих 90-нм продуктов серии Virtex-4 вдвое по сравнению с 130-нм процессорами, приняв триоксидную технологию и интегрированные функции платформы.![]()

Ратер из National Instruments отметил, что разработка FPGA также сталкивается с некоторыми проблемами, такими как время разработки, совместимость с отраслевыми спецификациями и выделение соответствующих ресурсов для разработки в области печатных плат и корпусов. Такие устройства, как NI CompactRIO (см. Фото), интегрируют FPGA, чтобы помочь в разработке продукта.

Рид из GE Fanuc очень заинтересован в компонентах ASSP, которые получены из различных традиционных конструкций ASIC. GE Fanuc использует доступные ядра IP (интеллектуальной собственности) для ПЛИС для повышения эффективности своей работы, производители используют ту же технологию, чтобы представить множество модифицированных версий стандартных компонентов для многих небольших рыночных областей. Рид заключил: «Мы можем запустить встроенный процессор, чтобы лучше соответствовать нужным нам функциям, и нам не нужно платить за функции, которые нам не нужны. Это потому, что IP-ядра можно использовать повторно. Мы можем быстро сопоставить эти IP-ядра. Сделано в стандартные компоненты. «

Сделано в стандартные компоненты. «

То, что мы пытаемся решить, — это спор между «специализированными интегральными схемами» и «программируемыми устройствами». Является ли окончательное решение гибридной технологией, давайте подождем и посмотрим

Про ASIC-и, FPGA-сики и ProASIC-и…

Как ранее было обещано, остановлюсь подробнее на уникальных в своем роде FPGA-представителях небольшой корпорации «Actel», которая насчитывает не более тысячи сотрудников по всему миру. Номенклатура ПЛИС, выпускаемых корпорацией «Actel», весьма широка и разнообразна: от «классических» FPGA в лице семейств ProASIC, ProASICPLUS, ProASIC3 до систем на кристалле (SoC), в лице семейств Fusion, SmartFusion и SmartFusion2. Линейка чипов семейства Fusion представляют собой нечто уникальное на сегодняшний день в области микроэлектроники — это объединение на одном кристалле внушительного блока ПЛИС, блока конфигурируемой аналоговой обработки, блоков ОЗУ, Flash-ПЗУ и даже встроенного CortexM3-контроллера с архитектурой ARM7 (присутствует в SmartFusion) !!! Таким образом на базе SmartFusion можно получить недорогое одночиповое и почти универсальное решение для построения широкого спектра управляющих, вычислительно-измерительных или коммутационных систем при вполне доступной стоимости в диапазоне от 20 до 50 у.

е. Также стоит обратить внимание, что корпорация «Actel» единственная, кто выпускает уникальные серии радиационно-стойких ПЛИС, востребованных в аэро-космической отрасли и военно-промышленном комплексе.

е. Также стоит обратить внимание, что корпорация «Actel» единственная, кто выпускает уникальные серии радиационно-стойких ПЛИС, востребованных в аэро-космической отрасли и военно-промышленном комплексе.

В отличие от всех других производителей FPGA-чипов, которые используют технологию SRAM (статического ОЗУ) конфигурирования чипа, «Actel» использует Flash-технологию для непосредственного хранения информации о конфигурации внутри элементарной ячейки FPGA. Отсюда вытекают основные преимущества FPGA-чипов производства «Actel» перед другими производителями: отсутствие необходимости переноса конфигурационной информации из внешнего энергонезависимого ППЗУ в коммутационную матрицу на основе статического ОЗУ; отсутствие бросков тока потребления при включении устройства, наблюдаемым при загрузке FPGA-чипов SRAM-технологии; отсутствие задержки при включении устройства, связанной с загрузкой конфигурации. Ну и самое главное преимущество FPGA от «Actel» — это повышенная надежность изделий данного производителя. FLASH-ячейка конфигурации в отличии от SRAM-ячейки на несколько порядков устойчивее к сбоям и рискам изменения конфигурации, вызванными, к примеру, влиянием электромагнитных помех. На рисунках ниже изображены схемно и как фрагмент топологии, ячейки конфигурационной матрицы, выполненные по SRAM-технологии и по FLASH-технологии.

FLASH-ячейка конфигурации в отличии от SRAM-ячейки на несколько порядков устойчивее к сбоям и рискам изменения конфигурации, вызванными, к примеру, влиянием электромагнитных помех. На рисунках ниже изображены схемно и как фрагмент топологии, ячейки конфигурационной матрицы, выполненные по SRAM-технологии и по FLASH-технологии.

Поскольку в элементарной ячейке памяти FLASH-типа используется всего 1 транзистор с плавающим затвором, то размеры ячейки уменьшаются и площадь, занятая такой ячейкой на кристалле, приблизительно в 7 раз меньше площади, занимаемой SRAM-ячейкой. Как следствие этого, снижается суммарный ток потребления кристалла и растет быстродействие таких микросхем. Технология FLASH-ПЛИС позволяет изготавливать микросхемы с рекордно низкими уровнями потребления в статическом режиме. На приведенных рисунках хорошо видны энергетические преимущества FPGA-чипов, изготовленных по FLASH-технологии перед аналогами, выполненными на SRAM-технологии.

Еще одно очень важное преимущество в использовании FLASH-технологии конфигурирования FPGA состоит в том, что в данном случае становится невозможно скопировать битовый поток конфигурационной информации, идущий в момент загрузки конфигурации от внешнего ППЗУ к FPGA. Для защиты интеллектуальной собственности проектов, в случае использования FPGA выполненных по SRAM-технологии, разработчикам приходится прибегать к различным схемно-программным ухищрениям. К примеру: типа установки дополнительных контроллеров или CPLD, шифрующих битовый поток данных либо подключать резервный источник питания для FPGA, обеспечивающий питание конфигурационной памяти в режиме микропотребления.

Для защиты интеллектуальной собственности проектов, в случае использования FPGA выполненных по SRAM-технологии, разработчикам приходится прибегать к различным схемно-программным ухищрениям. К примеру: типа установки дополнительных контроллеров или CPLD, шифрующих битовый поток данных либо подключать резервный источник питания для FPGA, обеспечивающий питание конфигурационной памяти в режиме микропотребления.

Техпроцесс изготовления сегодняшних FPGA (как и других устройств микроэлектроники) достиг уже 20-нм норм. А в ближайшей перспективе гигант микроэлектроники «Intel» собирается выпускать на своих заводах FPGA-чипы от «Altera» с нормами текхпроцесса 14 нм. Трудно себе даже представить масштабы прогресса микроэлектороники за прошедшие три десятка лет: первые микросхемы, выпущенные в 1979 году все тем же Intel, были разработаны на базе техпроцесса 3 мкм. Т.е. размеры элементарных структур микросхем уменьшились за это время более чем в 150 раз !!! Это позволяет сегодня размещать на кристаллах топовых семейств FPGA до десятка миллиардов транзисторов. Для сравнения: у 6-ти ядерного процессора Intel Sandy Bridge E (6C) насчитывается чуть более 2 млрд. транзисторов на кристалле. Согласно закону Мура, количество транзисторов, размещаемых на кристалле интегральной схемы, удваивается через каждые два года. Но сегодняшние технологии уже позволиили почти приблизиться к физическим пределам миниатюризации электронных схем. Еще совсем недавно уровень интеграции микросхем описывался понятиями БИС(большие интегральные схемы) и СБИС(сверхбольшие интегральные схемы), что соответствует сотням тысяч и нескольким миллионам логических вентилей на кристалле (вентиль реализуется на 4-ех эквивалентных транзисторах). Сейчас на некоторых чипах уже начитываются сотни миллионов вентилей на кристалле.

Для сравнения: у 6-ти ядерного процессора Intel Sandy Bridge E (6C) насчитывается чуть более 2 млрд. транзисторов на кристалле. Согласно закону Мура, количество транзисторов, размещаемых на кристалле интегральной схемы, удваивается через каждые два года. Но сегодняшние технологии уже позволиили почти приблизиться к физическим пределам миниатюризации электронных схем. Еще совсем недавно уровень интеграции микросхем описывался понятиями БИС(большие интегральные схемы) и СБИС(сверхбольшие интегральные схемы), что соответствует сотням тысяч и нескольким миллионам логических вентилей на кристалле (вентиль реализуется на 4-ех эквивалентных транзисторах). Сейчас на некоторых чипах уже начитываются сотни миллионов вентилей на кристалле.

Мда… Так вот, вернемся к нашим баранам, эээ … ASIC-ам.

Если основных представителей СБИС — таких как CPU и ПЛИС можно отнести к стандартному и программируемому пользователем типам, то на противоположном «полюсе» технологии СБИС располагаются ASIC(Application-Specific Integrated Circuit), т. е. разрабатываемые только для выполнения конкретных задач пользователя — заказные микросхемы. Это, как правило, крупносерийные устройства типа «система на кристалле», заказываемые производителями электроники для удешевления своих изделий. Непосредственное серийное производство ASIC-чипов обходится намного дешевле, чем производство FPGA-чипов — в силу отсутствия дорогостоящей SRAM-конфигурационной памяти или в случае FPGA от «Actel» — более дешовой Flash-памяти. Но процесс подготовки производства нового ASIC-чипа несоразмерно дороже и длительнее, чем в случае разработки нового семейства FPGA. С точки зрения конечного пользователя, ASIC-чипы в отличии от FPGA, не нуждаются в загрузке конфигурационной информации и следовательно отсутствует возможность скопировать интеллектуальную собственность проекта внутри микросхемы ASIC. Также как и FPGA, микросхемы ASIC могут иметь встроенные блоки быстродействующей памяти. ASIC-микросхемам не грозит частичный сбой конфигурации, как в случае с FPGA, изготоленных по SRAM-технологии, так как связи межсоединений внутри ASIC-микросхемы непосредственные и неупраляемые.

е. разрабатываемые только для выполнения конкретных задач пользователя — заказные микросхемы. Это, как правило, крупносерийные устройства типа «система на кристалле», заказываемые производителями электроники для удешевления своих изделий. Непосредственное серийное производство ASIC-чипов обходится намного дешевле, чем производство FPGA-чипов — в силу отсутствия дорогостоящей SRAM-конфигурационной памяти или в случае FPGA от «Actel» — более дешовой Flash-памяти. Но процесс подготовки производства нового ASIC-чипа несоразмерно дороже и длительнее, чем в случае разработки нового семейства FPGA. С точки зрения конечного пользователя, ASIC-чипы в отличии от FPGA, не нуждаются в загрузке конфигурационной информации и следовательно отсутствует возможность скопировать интеллектуальную собственность проекта внутри микросхемы ASIC. Также как и FPGA, микросхемы ASIC могут иметь встроенные блоки быстродействующей памяти. ASIC-микросхемам не грозит частичный сбой конфигурации, как в случае с FPGA, изготоленных по SRAM-технологии, так как связи межсоединений внутри ASIC-микросхемы непосредственные и неупраляемые. Но за все эти преимущества приходится платить длительными сроками разработки и внушительными бюджетами подготовки производства. Применение микросхем ASIC становится экономически оправданным в случае достаточно большого тиража продукции, так как финансово-трудовые издержки, затраченные на разработку и отладку проекта заказчика очень масштабны. Поскольку требуется очень тщательная верификация проектов, то и сроки отладки проектов могут быть намного больше, чем при отладке проектов для FPGA. Еще один недостаток (пожалуй, самый серьезный…) микросхем ASIC связан с тем, что они не могут быть переконфигурированы. Поэтому любая модернизация изделия, содержащего на борту ASIC-микросхемы, сопряжена со значительными трудностями.

Но за все эти преимущества приходится платить длительными сроками разработки и внушительными бюджетами подготовки производства. Применение микросхем ASIC становится экономически оправданным в случае достаточно большого тиража продукции, так как финансово-трудовые издержки, затраченные на разработку и отладку проекта заказчика очень масштабны. Поскольку требуется очень тщательная верификация проектов, то и сроки отладки проектов могут быть намного больше, чем при отладке проектов для FPGA. Еще один недостаток (пожалуй, самый серьезный…) микросхем ASIC связан с тем, что они не могут быть переконфигурированы. Поэтому любая модернизация изделия, содержащего на борту ASIC-микросхемы, сопряжена со значительными трудностями.

Все СБИС (включая CPU, ПЛИС и ASIC) имеют структуру слоистого коржевого торта. Эти «коржики» изготавливаются при помощи фотошаблонов (или масок). В современных техпроцессах при производстве СБИС может применяться до полусотни масок, определяющих базовые структуры, слои металлизации и изоляции. Самые нижние базовые слои содержат минимальные конструктивные элементы структуры — транзисторы. Следующие слои содержат наборы металлических проводников, определяющих топологию соединений для формирования базовых логических блоков (вентили, триггеры, сумматоры) и слои изоляции. А далее весь этот «тортик»

Самые нижние базовые слои содержат минимальные конструктивные элементы структуры — транзисторы. Следующие слои содержат наборы металлических проводников, определяющих топологию соединений для формирования базовых логических блоков (вентили, триггеры, сумматоры) и слои изоляции. А далее весь этот «тортик» обмазывается кремом … финишно коммутируется на самых верхних уровнях для достижения конечной требуемой функциональности. Ниже на правом рисунке в разрезе оранжевым цветом показаны участки медных соединительных проводников.

Процесс изготовления масок-фотошаблонов очень дорогой и длительный: Например, для техпроцесса 45 нм стоимость комплекта масок может достигать миллиона долларов и выше, а суммарный срок разработки и подготовки производства ASIC-чипа может составлять более года.

Различают ASIC-микросхемы полностью заказные (Full Custom) и полузаказные (Semi-Custom). Первые разрабатываются с нуля, т.е. начиная с разработки базовых транзисторных слоев. Вторые разрабатываются на основе базовых логических блоков и требуют только изготовления необходимых слоев металлизации и изоляции. При изготовлении Full Custom ASIC-микросхем разработчик имеет полную свободу действий и схемотехнических решений. В разультате на выходе могут быть получены наилучшие технические характеристики (быстродействие, энергоэффективность) и наилучшая степень использования кристалла. Полузаказные ASIC-микросхемы, в свою очередь изготавливаются на:основе вентильных матриц либо набора стандартных ячеек. Полузаказные ASIC на основе стандартных ячеек требуют изготовления полного комплекта фотошаблонов, но используют элементы стандартных библиотек схемных решений. Таким образом упрощается и удешевляется процесс изготовления базового слоя (базовый кристалл), что значительно сказывается на общей картине подготовки технологического процесса. По сравнению с Full Custom ASIC, эти полузаказные СБИС имеют менее выдающиеся технические характеристики, но позволяют вдвое уменьшить сроки разработки.

Вторые разрабатываются на основе базовых логических блоков и требуют только изготовления необходимых слоев металлизации и изоляции. При изготовлении Full Custom ASIC-микросхем разработчик имеет полную свободу действий и схемотехнических решений. В разультате на выходе могут быть получены наилучшие технические характеристики (быстродействие, энергоэффективность) и наилучшая степень использования кристалла. Полузаказные ASIC-микросхемы, в свою очередь изготавливаются на:основе вентильных матриц либо набора стандартных ячеек. Полузаказные ASIC на основе стандартных ячеек требуют изготовления полного комплекта фотошаблонов, но используют элементы стандартных библиотек схемных решений. Таким образом упрощается и удешевляется процесс изготовления базового слоя (базовый кристалл), что значительно сказывается на общей картине подготовки технологического процесса. По сравнению с Full Custom ASIC, эти полузаказные СБИС имеют менее выдающиеся технические характеристики, но позволяют вдвое уменьшить сроки разработки. При технологии полузаказных ASIC на основе вентильных матриц используются готовые стандратные схемные полуфабрикаты, называемые базовыми кристаллами, которые дополняются слоями межсоединений. В даном случае требуется изготовить гораздо меньшее количество фотошаблонов. Результирующие технические характеристи такого чипа получаются еще дальше от оптимума, но сроки разработки могут быть сокращены в трое-четверо. На сегодняшний день полузаказные ASIC-микросхемы эволюционировали в отдельный подвид сруктурированных ASIC, которые могут включать в свою структуру функционально завершенные блоки, как то: ядра процессоров, различные контроллеры или модули памяти. В этом сегменте есть весьма интересное решение, разработанное корпорацией «eASIC» — новое поколение структурированных ASIC-чипов под названием Nextreme. По заявлениям корпорации «eASIC», структурированные ASIC Nextreme позволяют сократить срок разработки до 1 месяца при отсутствии ограничения на минимальное количество выпускаемых изделий, имея при этом FPGA-подобную архитектуру ! Но о них я пожалуй расскажу отдельно другим разом, а то и так уже «многа букафф»

При технологии полузаказных ASIC на основе вентильных матриц используются готовые стандратные схемные полуфабрикаты, называемые базовыми кристаллами, которые дополняются слоями межсоединений. В даном случае требуется изготовить гораздо меньшее количество фотошаблонов. Результирующие технические характеристи такого чипа получаются еще дальше от оптимума, но сроки разработки могут быть сокращены в трое-четверо. На сегодняшний день полузаказные ASIC-микросхемы эволюционировали в отдельный подвид сруктурированных ASIC, которые могут включать в свою структуру функционально завершенные блоки, как то: ядра процессоров, различные контроллеры или модули памяти. В этом сегменте есть весьма интересное решение, разработанное корпорацией «eASIC» — новое поколение структурированных ASIC-чипов под названием Nextreme. По заявлениям корпорации «eASIC», структурированные ASIC Nextreme позволяют сократить срок разработки до 1 месяца при отсутствии ограничения на минимальное количество выпускаемых изделий, имея при этом FPGA-подобную архитектуру ! Но о них я пожалуй расскажу отдельно другим разом, а то и так уже «многа букафф»

Некоторые корпорации, специализирующиеся на выпуске ПЛИС, также выпускают полузаказные ASIC, на основе свох базовых матричных кристаллов — например, серия HardCopy от «Altera» позиционируется как более дешевое решение в проектах, использующих FPGA-кристаллы топового семейства Stratix (II — V). К слову, HardCopy могут использоваться как прямая замена данных FPGA-чипов от «Altera», так как они полностью повторяют архитектуру соответствующих FPGA-чипов и совместимы по расположению выводов. Если сравнивать технические характеристики полузаказных ASIC и FPGA на примере тех же HardCopy и их FPGA-прототипов, то тут улучшение основных показателей может достигать до 50%. В большей степени это обусловлено непосредственными связями внутри кристалла и межсоединений, так как уменьшаются длины участков соединений и уменьшаются задержки распространения сигналов. Следовательно увеличивается быстродействие и уменьшается энергопотребление ASIC-чипов

К слову, HardCopy могут использоваться как прямая замена данных FPGA-чипов от «Altera», так как они полностью повторяют архитектуру соответствующих FPGA-чипов и совместимы по расположению выводов. Если сравнивать технические характеристики полузаказных ASIC и FPGA на примере тех же HardCopy и их FPGA-прототипов, то тут улучшение основных показателей может достигать до 50%. В большей степени это обусловлено непосредственными связями внутри кристалла и межсоединений, так как уменьшаются длины участков соединений и уменьшаются задержки распространения сигналов. Следовательно увеличивается быстродействие и уменьшается энергопотребление ASIC-чипов

Подведем итоги:

1. FPGA-чипы:

+ являются универсальным схемотехническим решением и могут быть легко и быстро адаптированы под выполнение практически любой задачи или алгоритма

— уступают по основным техническим характеристикам полузаказным и тем более полностью заказным ASIC-ам. Относительно дороги чипы топовых серий

2. ASIC-чипы:

ASIC-чипы:

+ хороши только для строго конкретных задач, под которые они и изготовлены, обладая при этом наилучшими показателями в сравнении с другими возможными решениями. Наименьшее энергопотребление и наибольшее быстродействие. Низкая себестоимость.готовых чипов.

— астрономически дороги на этапе подготовки производства и могут себя быстро окупить только при масштабных тиражах. Длительный процесс подготовки производства. Заказываются только большими партиями (десятки тысяч штук)

3. Применительно к майнингу, конечно же ASIC-и весьма заманчивы, но на мое IMHO — как-то это все очень сомнительно и маловероятно… Full Custom ASIC-микросхемы могут себе позволить немногие производители электроники. Так что, в данном контексте могут всерьез рассматриваться разве что полузаказные ASIC-чипы типа HardCopy от Altera. Но, опять же, смотря с какими тиражами работать.

Ну вот вроде бы и все, чем хотелось поделиться. Надеюсь что информация будет многим полезна …

В чем разница между ASIC и FPGA — Разница Между

главное отличие между AIC и FPGA в том, что AIC используется для выполнения конкретной задачи, а FPGA используется для выполнения различных задач. Электронная схема — это структура или канал, который

Электронная схема — это структура или канал, который

главное отличие между ASIC и FPGA в том, что ASIC используется для выполнения конкретной задачи, а FPGA используется для выполнения различных задач.

Электронная схема — это структура или канал, который соединяет множество электронных компонентов, таких как резисторы и транзисторы, с помощью проводов или дорожек. Электрический ток протекает через компоненты этой цепи. ASIC и FPGA — две технологии для построения электрических цепей.

Ключевые области покрыты

1. Что такое ASIC

— определение, особенности

2. Что такое ПЛИС?

— определение, особенности

3. В чем разница между ASIC и FPGA

— Сравнение основных различий

Основные условия

ASIC, FPGA

Что такое ASIC

ASIC выступает за Специализированная интегральная схема, Можно настроить его для использования для конкретной задачи. Он состоит из около 100 миллионов логических элементов. Разработчики ASCI используют языки описания оборудования для описания его функциональных возможностей.

Он состоит из около 100 миллионов логических элементов. Разработчики ASCI используют языки описания оборудования для описания его функциональных возможностей.

Большинство ASIC состоит из микропроцессоров, модулей памяти (ROM, RAM, EEPROM) и т. Д. System On Chip (SoC) является ASIC с этими компонентами. Обычно ASIC больше подходит для применения в устройствах с большими объемами производства. Обычно рекомендуется разрабатывать и тестировать схему с использованием FPGA, прежде чем внедрять ее на ASIC.

Что такое ПЛИС?

ПЛИС выступает за Полевой программируемый массив ворот, Он предоставляет большое количество логических ресурсов для реализации схем. В современных ПЛИС доступно около 330 000 логических блоков с 1100 входами и выходами. Пользователи могут перепрограммировать ПЛИС в соответствии с требованиями и спецификацией схемы.

Обычно ПЛИС состоит из программируемых логических блоков, соединений и блоков ввода-вывода. ПЛИС имеет массив программируемых логических блоков. Большинство логических блоков также содержат элементы памяти, такие как триггеры. Реконфигурируемые межсоединения позволяют соединять эти блоки вместе. Кроме того, блоки ввода-вывода помогают устанавливать соединения вне кристалла. Мы можем настроить логические блоки для выполнения простых функций, таких как операция AND, а также для реализации сложной системы, такой как многоядерный процессор.

ПЛИС имеет массив программируемых логических блоков. Большинство логических блоков также содержат элементы памяти, такие как триггеры. Реконфигурируемые межсоединения позволяют соединять эти блоки вместе. Кроме того, блоки ввода-вывода помогают устанавливать соединения вне кристалла. Мы можем настроить логические блоки для выполнения простых функций, таких как операция AND, а также для реализации сложной системы, такой как многоядерный процессор.

Разница между ASIC и FPGA

Определение

ASIC — это интегральная схема, настроенная для конкретного использования, а не для задач общего назначения. FPGA, с другой стороны, представляет собой интегральную схему, разработанную для конфигурации заказчиком или разработчиком после изготовления. Это основное отличие ASIC от FPGA.

Длинная форма

Длинная форма для ASIC — Интегральная схема для конкретного применения, в то время как FPGA расшифровывается как программируемый полевой вентильный массив.

модификация

Кроме того, модификации являются основным отличием ASIC и FPGA. После создания невозможно изменить ASIC. С другой стороны, возможно модифицировать FPGA.

Приложения

Кроме того, ASIC может применяться для устройств с большими объемами производства, в то время как FPGA подходит для создания прототипов и устройств с небольшими объемами производства. Это еще одно различие между ASIC и FPGA.

Стоимость материала

Кроме того, ASIC требует меньше материалов по сравнению с FPGA, поэтому периодические затраты на ASIC низкие.

Заключение

ASIC — это интегральная схема, которая может быть настроена для выполнения определенной задачи, в то время как FPGA представляет собой интегральную схему, которая содержит логические блоки и соединения. Основное различие между ASIC и FPGA заключается в том, что ASIC используется для выполнения конкретной задачи, а FPGA используется для выполнения различных задач.

Ссылка:

1. «Интегральная схема для конкретного приложения». Википедия, Фонд Викимедиа, 26 декабря 2018 г.

Экономически выгодная замена FPGA на ASIC. Быстрая разработка и постановка на производство заказных микросхем от корпорации Toshiba

Фирма МТ-Систем предлагает крупным клиентам интегральные микросхемы, выполненные на заказ (ASIC), на мощностях корпорации Toshiba, в качестве экономически выгодной замены ПЛИС.

Благодаря запатентованной технологии Fit Fast Structured Arrays (FFSA™ европейское название Ultimate Platform SoC (UPSoC)) заказчик получает следующие технико-экономические преимущества:

- Единовременные затраты на проектирование (NRE) уменьшены в 5 раз в сравнении с технологией разработки на стандартах ячейках (standard cell ASIC).

- Ускоренный вывод микросхемы на рынок: до 5 недель из прототипа, описанного на уровне регистровых передач (RTL).

- Уменьшение рисков, благодаря использованию проверенных IP-ядер и методов.

- Простата внесение изменений

- Разработка нескольких ASIC на одной платформе

- Гибкость настройки вводов-выводов на подобии FPGA

- Гибкое конфигурирование памяти (ROM, SP, DP RAMs).

- Поддержка перевода проекта из ПЛИС Altera и Xilinх с сохранением с совместимости по корпусу

- Производительность увеличивается до 5 раз по сравнению с ПЛИС

- Снижение энергопотребления от 8 до 16 раз по сравнению с ПЛИС

Этапы разработки/производства заказной ASIC

В основе технологии FFSA™, обеспечивающей выше приведенные преимущества, лежит использование кристаллов с заранее сформированными блоками, которые конфигурируются с минимальными усилиями, с помощью дополнительных заказных слоев металлизации.

В состав блоков входят массивы вентилей и память. Заказчикам доступны специализированные IP-ядра: процессоров ARM; внутренних шин; интерфейсов и DSP.

Общая стоимость продукции (TTL), рассчитывается как:

На ПЛИС (FPGA):

TTL = PP * QTY, PP – стоимость заказа микросхемы FPGA.

По технологии FFSA™:

TTL = NRE + SP * QTY, где QTY: количество, SP: стоимость производства.

Например, для продукции из нижнего ценового сегмента рынка (Low End):

Замена FPGA

| |

TTL=$13*20*10 =$2.6M | |

FFSA NRE: $0,3M $8*20*10=$1.6M TTL=$0.3M+$1.6M=$1.9M | |

Выгода: $2.6M-$1.9M=$0.7M Экономия: (0.7/2.6)*100=27% |

Для продукции из верхнего ценового сегмента рынка (High End):

Замена FPGA

| |

TTL=$10*10*5 =$5M | |

FFSA NRE: $0,3M $60*10*5=$3M TTL=$0.3M+$3M=$3.3M | |

Выгода: $5M-$3.3M=$1.7M Экономия: (1.7/5)*100=34% |

Как видно из рисунка порог равнозначной стоимости изделий для High End продукции наступает уже от 6000 изделий за весь жизненный цикл продукции.

За подробной информацией обращайтесь:

[email protected]

+7 (812) 325-3685 доб.1414

Перевод — Кладбище «ASIC/FPGA-защищённых» решений и необходимость в сдвиге парадигмы

Любому, наблюдающему за развитием алгоритмов майнинга на базе Cryptonight, очевидна одна простая вещь: заявления об устойчивости к ASIC-майнингу просто не укладываются в историческую реальность. Как по мне, существующий подход напоминает что-то вроде: «Мама, смотри, я могу без рук!» То есть, разработчики алгоритмов задаются вопросом: «А может ASIC могут делать X?» Ну а потом они обнаруживают, что сильно заблуждались. И такой подход просто не работает. Могут ли FPGA выполнять команды с плавающей запятой?

Ну конечно же, могут. Фактически в случае с HPC — это маркетинговый параметр, как пробег в милях на галлон израсходованного топлива для автомобиля, а следовательно, вы с лёгкостью найдёте теоретические значения TFLOPS в буклете производителя.

Так что, давайте так и сделаем: «Intel может похвастаться созданием FPGA-чипа, выдающего 10 TFLOPS» [1]. Продолжим… Vega 64 делает все 12,5 TLOPS [2]…

Чтобы узнать хэшрейт CN-GPU, возьмём TFLOPS и помножим их на 125. Просто прекрасно, не так ли?

Что за чёрт??? Ведь FPGA так быстро работают с другими алгоритмами!!!

Систематические ошибки при написании алгоритмов, а именно попытки создать тяжёлый с точки зрения памяти алгоритм, при реализации которого FPGA можно конфигурировать так, что она будет получать доступ к памяти в 100 раз быстрее, чем CPU, привели к тому, что разработчики алгоритма Monero уверовали в то, что FPGA — это некие метафизические объекты, никак не связанные законами физики.

В реальности, работа с плавающей запятой сокращает физическое количество ядер для работы с плавающей точкой на чипе. GPU, по природе своей используемые для вычисления… ммм… графики (помните те старые добрые времена, когда мы покупали GPU, чтобы рубиться в Crisis?), имеют их в избытке. Вот почему графическая плата за $500 даст фору FPGA за $1000 по TFLOPS.

Можно ли взять плату GPU и убрать из неё всё, кроме FP-ядер? Безусловно. Но тогда надо спросить себя: сколько можно убрать? 20%, 50%, 75%? Допустим, что последний вариант. Тогда кто купит схему ASIC за $6000, выдающую хэшрейт всего в 4 раза больший, чем у Vega 64 за $500?

Зал славы (а также опасений, неуверенности и сомнений) Monero

Как известно всем, кто причастен к Ryo, если сообщество Monero чувствует угрозу в том, чем мы занимаемся, оно начинает отчаянно лягаться. Так что, предлагаю зацепиться за такую «реакцию» и притвориться, что она конструктивна. Ну а почему бы и нет, в самом-то деле? =)

Я не могу прочитать исходник! Выложите описание!

У CN-GPU нет описания и опубликованного логического обоснования проекта — только исходный код, так что пока я ничего не могу сравнивать. Всё, что я понял к этому моменту, так это то, что CN-GPU — это совсем не Cryptonight. Слишком много частей алгоритма подверглось изменениям. К тому же, он много потребляет на GPU, а с CPU не работает, что противоречит тому, что было написано в оригинальном официальном документе Monero. [SChernykh] [3]

Я всегда рад помочь тем, у кого возникают проблемы со чтением исходного кода, и этот раз — не исключение =). В целом, как оказалось, что энергия потребляется на одном уровне с MoneroV8.

Наша культура круче вашей!

Те, кто интересуются «культурой проекта» и «стилем разработки», могут сравнить соответствующее обсуждение на Monero GitHub с историей возникновения алгоритма доказательства работы CN-GPU, который для тех, кто не в курсе, просто появился из ниоткуда в виде законченного кода. [rbrunner7] [4]

Мы — небольшая команда профессионалов, и нам нравится быстро продвигаться вперёд. Мы предпочитаем взвешенно работать над решением реальных вопросов, а не с волшебной комбинацией двоичных разрядов, вроде MoneroV7.

А давайте устроим мешанину из умных технических терминов в надежде потрясти читателя!

FPGA фундаментально отличается от ASIC. FLOP — не защитит от ASIC, а существующий паттерн говорит о росте применения ASIC.

Так как я ничего не слышал о критическом обзоре «CN»-GPU, я смею предположить, что «особенность» кроется где-то в математической подноготной, позволяющей ASIC пропускать определённые значения или просто производить недействительные хэши, так как общий (действительный) хэшрейт повышается в разы. [Leza89] [5]

Из первого параграфа ясно, что он не совсем уловил смысл сдвига парадигмы, и полагает, что защита состоит в том, что ASIC потребуется «помощь» для вычислений с плавающей точкой, точно так же, как RandomX полагает, что «помощь» требуется для дешифровки команд.

Второй параграф — хороший пример того, что мы часто указываем в квадрате B3 Bullshit-бинго Monero. Я знал «членов сообщества Monero» (квадрат B1), пытавшихся одурачить остальных, предлагая фейковые результаты исследований [6]. Другой пример можно найти здесь [7]. Воспринимайте это, как хотите, но лично я считаю, что тут демонстрируется полное неуважение к собственному сообществу.

Источник: Cryptonight-GPU — FPGA-proof PoW algorithm based on floating point instructions

Перевод:

Mr. Pickles (@v1docq47)

Редактирование:

Agent LvM (@LvMi4)

Коррекция:

Kukima (@Kukima)

FPGA против ASIC: разница между ними и какой из них использовать?

VL82C486 Однокристальная микросхема системного контроллера 486 ASIC. Источник: Википедия

Введение

Для человека, плохо знакомого с областью проектирования СБИС и аппаратного обеспечения, часто возникает один из первых вопросов: в чем разница между FPGA, ASIC и CPLD? В другом посте мы попытались ответить на различия между FPGA и CPLD. В этой статье будет определено, что такое FPGA и что такое ASIC, и мы попытаемся прояснить вопросы о FPGA и ASIC, мы рассмотрим сходства и различия между ними.Мы обозначим преимущества и недостатки каждого из них, чтобы вы могли принять осознанное решение, какой из них использовать в зависимости от потребностей вашего приложения.

Вот оглавление, чтобы вы могли легко перейти к интересующей вас подтеме.

Содержимое:

Что такое ПЛИС?

FPGA — это программируемая вентильная матрица. Это интегральная схема, которую можно «в полевых условиях» запрограммировать для работы в соответствии с предполагаемой конструкцией. Это означает, что он может работать как микропроцессор, или как блок шифрования, или как видеокарта, или даже все три сразу.Как следует из самого названия, ПЛИС программируется на месте. Таким образом, FPGA, работающая как микропроцессор, может быть перепрограммирована для работы в качестве графической карты в полевых условиях, а не на заводах по производству полупроводников. Проекты, работающие на ПЛИС, обычно создаются с использованием языков описания оборудования, таких как VHDL и Verilog.

ПЛИСсостоит из тысяч конфигурируемых логических блоков (CLB), встроенных в океан программируемых межсоединений. CLB в основном состоят из справочных таблиц (LUT), мультиплексоров и триггеров.Они могут реализовывать сложные логические функции. Помимо CLB и межкомпонентных соединений маршрутизации, многие FPGA также содержат выделенные твердые кремниевые блоки для различных функций, таких как блочная RAM, блоки DSP, контроллеры внешней памяти, PLL, мультигигабитные трансиверы и т. Д. Недавняя тенденция заключается в предоставлении аппаратно-кремниевых процессоров. ядро (например, ARM Cortex A9 в случае Xilinx Zynq) внутри одного и того же кристалла FPGA, так что процессор может решать рутинные, некритические задачи, тогда как FPGA может заботиться о высокоскоростном ускорении, которое не может быть выполнено с помощью процессоров.Эти выделенные аппаратные блоки критически важны для конкуренции с ASIC.

Что такое ASIC?

ASIC — это специализированная интегральная схема. Как следует из названия, ASIC зависят от приложения. Они предназначены для одной единственной цели и функционируют одинаково на протяжении всего срока службы. Например, процессор в вашем телефоне — это ASIC. Он предназначен для работы в качестве ЦП на протяжении всей своей жизни. Его логическую функцию нельзя изменить ни на что другое, потому что его цифровая схема состоит из постоянно подключенных вентилей и триггеров на кремнии.Логическая функция ASIC определяется так же, как и в случае FPGA, с использованием языков описания оборудования, таких как Verilog или VHDL. Разница в случае ASIC заключается в том, что результирующая схема постоянно втягивается в кремний, тогда как в FPGA схема создается путем соединения ряда настраиваемых блоков. Для сравнения, подумайте о создании замка из блоков Lego по сравнению с созданием замка из бетона. Первый аналогичен FPGA, тогда как последний аналогичен ASIC.Вы можете повторно использовать блоки Lego, чтобы создать другой дизайн, но бетонный замок останется навсегда.

Сводка сравненияFPGA и ASIC

| № | FPGA | ASIC |

|---|---|---|

| 1 | Реконфигурируемая схема. ПЛИС можно перенастроить с другим дизайном. У них даже есть возможность перенастроить часть микросхемы, в то время как остальные области микросхемы все еще работают! Эта функция широко используется в ускоренных вычислениях в центрах обработки данных. | Постоянная схема. После того, как специфическая для приложения схема приклеена к кремнию, ее нельзя будет изменить. Схема будет работать так же в течение всего срока службы. |

| 2 | Дизайн обычно определяется с использованием языков описания оборудования (HDL), таких как VHDL или Verilog. | То же, что и для ПЛИС. Дизайн указывается с использованием HDL, такого как Verilog, VHDL и т. Д. |

| 3 | Более легкий входной шлагбаум. Начать разработку FPGA можно всего за 30 долларов США. | Очень высокий входной барьер с точки зрения затрат, кривой обучения, взаимодействия с литейным производством полупроводников и т. Д. Начало разработки ASIC с нуля может обойтись в миллионы долларов. |

| 4 | Не подходит для массового производства в очень больших объемах. | Подходит для массового производства в очень больших объемах. |

| 5 | Менее энергоэффективен, требует больше энергии для той же функции, которую ASIC может выполнить при более низкой мощности. | Намного более энергоэффективный, чем FPGA.Энергопотребление ASIC можно очень точно контролировать и оптимизировать. |

| 6 | Ограниченная рабочая частота по сравнению с ASIC аналогичного технологического узла. Маршрутизация и настраиваемая логика съедают запас по времени в ПЛИС. | ASIC, изготовленная с использованием одного и того же технологического узла, может работать на гораздо более высокой частоте, чем FPGA, поскольку ее схема оптимизирована для ее конкретной функции. |

| 7 | Аналоговые конструкции с ПЛИС невозможны.Хотя ПЛИС могут содержать определенное аналоговое оборудование, такое как ФАПЧ, АЦП и т. Д., Они не очень гибки для создания, например, радиопередатчиков. | ASIC могут иметь полную аналоговую схему, например приемопередатчик WiFi, на одном кристалле вместе с ядрами микропроцессора. Это преимущество, которого нет в FPGA. |

| 8 | ПЛИС хорошо подходят для таких приложений, как радары, базовые станции сотовых телефонов и т. Д., Где может потребоваться модернизация существующей конструкции для использования лучшего алгоритма или до лучшей конструкции.В этих приложениях высокая стоимость ПЛИС не является решающим фактором. Напротив, решающим фактором является возможность программирования. | ASIC определенно не подходят для областей применения, в которых может потребоваться частое или периодическое обновление конструкции. |

| 9 | Предпочтительно для создания прототипов и проверки дизайна или концепции. Многие ASIC созданы с использованием самих ПЛИС! Сами основные производители процессоров используют ПЛИС для проверки своих систем на кристалле (SoC).С помощью прототипирования ПЛИС легче убедиться, что проект работает правильно, как задумано. | Не рекомендуется создавать прототипы дизайна с использованием ASIC, если они не прошли полную проверку. После того, как силикон заклеен, почти ничего нельзя сделать, чтобы исправить ошибку конструкции (за исключением случаев). |

| 10 | Разработчикам FPGA обычно не нужно заботиться о внутреннем дизайне. Все обрабатывается инструментами синтеза и маршрутизации, которые гарантируют, что дизайн работает, как описано в коде RTL, и соответствует времени.Таким образом, дизайнеры могут сосредоточиться на выполнении RTL-дизайна. | Разработчики ASIC должны заботиться обо всем, от RTL до дерева сброса, дерева часов, физической схемы и маршрутизации, узла процесса, производственных ограничений (DFM), ограничений тестирования (DFT) и т. Д. Как правило, каждая из упомянутых областей обрабатывается другой специалист. |

Визуальное сравнение FPGA и ASIC

Анализ стоимостиFPGA и ASIC

Согласно Радживу Джаяраману из Xilinx [1], график анализа стоимости ASIC и FPGA выглядит так, как показано выше.Стоимость и стоимость единицы не указаны в таблице, поскольку они различаются в зависимости от используемой технологии процесса и времени. У ASIC очень высокие затраты на непериодическое проектирование (NRE), исчисляемые миллионами, тогда как фактическая стоимость кристалла может быть в центах. В случае ПЛИС нет затрат на NRE. Вы платите за фактическую микросхему FPGA и, как правило, получаете бесплатное программное обеспечение для этой FPGA (до определенного предела). Итак, общая стоимость ASIC начинается с очень высокой стоимости из-за стоимости NRE, но ее наклон более пологий. То есть создание прототипов ASIC в небольших количествах очень дорого, но в больших объемах стоимость одного объема становится намного меньше.В случае FPGA стоимость IC значительно выше, поэтому при больших объемах она становится дорогостоящей по сравнению с ASIC.

Вот разбивка компонентов стоимости ASIC:

- Инструменты и обучение ASIC EDA

- Стоимость проектирования

- Стоимость ДПФ

- Стоимость моделирования

- ASIC Masks Стоимость

- Стоимость вафли

- Обработка пластин

- Утилизация штампа

- Доходность и производственные убытки

- Упаковка

По сравнению с приведенным выше списком, стоимость FPGA указана только для IC, которую можно купить в готовом виде.

Как выбрать между ПЛИС или ASIC

Вы новичок и хотите узнать больше о СБИС и проектировании оборудования? Тогда вам больше всего подойдут FPGA и программное обеспечение для моделирования. Вы разрабатываете свой собственный продукт? Прохладный! Спросите себя, каков целевой рынок, ожидаемый ценовой диапазон, бюджет мощности, требования к скорости и т. Д. Для продукта. Можно ли это сделать с помощью ПЛИС? Если да, то приступайте к созданию прототипа своей идеи. В противном случае у вас может не быть другого выхода, кроме как использовать ASIC. В большинстве случаев должна быть возможность по крайней мере прототипировать и проверять вашу идею с помощью FPGA.И к тому времени, когда вы закончите с прототипом, вы сами поймете, нужно ли вам идти по маршруту ASIC или нет. Конечно, если ваш дизайн является совершенно революционным и необычным с очень специфическими требованиями (с точки зрения стоимости, мощности, скорости и т. Д.), У вас нет другого выбора, кроме как пойти по маршруту ASIC. В противном случае FPGA могут удовлетворить большинство случаев использования, особенно когда вам нужно реконфигурируемое оборудование.

Итак, поехали! Мы надеемся, что теперь вы лучше осведомлены о FPGA и ASIC и сможете принять осознанное решение о том, какой из них выбрать, в зависимости от потребностей вашего приложения!

Список литературы

- Раджив Джаяраман, Xilinx Inc, 2001 https: // www.doc.ic.ac.uk/~wl/teachlocal/arch/killasic.pdf

Узнайте разницу между FPGA и ASIC за 15 минут — FPGA Technology

ПЛИСсобирается заменить ASIC, это девиз, который производители ПЛИС кричат уже более десяти лет. Тем не менее, доля рынка ПЛИС сильно возросла, а ASIC по-прежнему развлекаются. В чем разница между FPGA и ASIC? FPGAKey подробно проанализирует для всех желающих.

1.Введение