PCI Express 1x, 4x, 8x, 16x bus распиновка и описание @ pinouts.ru

PCI Express as a high-bandwidth, low pin count, serial, interconnect technology. It was designed to replace the older PCI and AGPbus standards. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. PCI Express architecture provides a high performance I/O infrastructure for Desktop Platforms with transfer rates starting at 2.5 Giga transfers per second over a x1 PCI Express lane for Gigabit Ethernet, TV Tuners, Firewire 1394a/b controllers, and general purpose I/O. PCI Express architecture provides a high performance graphics infrastructure for Desktop Platforms doubling the capability of existing AGP8x designs with transfer rates of 4.0 Gigabytes per second over a x16 PCI Express lane for graphics controllers. A lane is composed of two differential signaling pairs, with one pair for receiving data and the other for transmitting.

ExpressCard utilizing PCI Express interface, developed by the PCMCIA group for mobile computers. PCI Express Advanced Power Management features help to extend platform battery life and to enable users to work anywhere, without an AC power source. The PCI Express electrical interface is also used in some computer storage interfaces SATA Express and M.2.

The broad adoption of PCI Express in the mobile, enterprise and communication segments enables convergence through the re-use of a common interconnect technology.

PCI-E is a serial bus which uses two low-voltage differential LVDS pairs, at 2.5Gb/s in each direction [one transmit, and one receive pair]. PCI Express supports 1x [2.5Gbps], 2x, 4x, 8x, 12x, 16x, and 32x bus widths [transmit / receive pairs].

The differential pins [Lanes] listed in the pin out table above are LVDS which stands for: Low Voltage Differential Signaling.

PCI-Express 1x Connector Pin-Out

| Pin |

Side B Connector |

Side A Connector |

||

| # | Name | Description | Name | Description |

| 1 | +12 volt power | PRSNT#1 | Hot plug presence detect | |

| 2 | +12v | +12 volt power | +12v | +12 volt power |

| 3 | +12v | +12 volt power | +12v | +12 volt power |

| 4 | GND | Ground | GND | Ground |

| 5 | SMCLK | SMBus clock | JTAG2 | TCK |

| 6 | SMDAT | SMBus data | JTAG3 | TDI |

| 7 | GND | Ground | JTAG4 | TDO |

| 8 | +3.3v | +3.3 volt power | JTAG5 | TMS |

| 9 | JTAG1 | +TRST# | +3.3v | +3.3 volt power |

| 10 | 3.3Vaux | 3.3v volt power | +3.3v | +3.3 volt power |

| 11 | WAKE# | Link Reactivation | PWRGD | Power Good |

|

Mechanical Key |

||||

| 12 | RSVD | Reserved | GND | Ground |

| 13 | GND | Ground | REFCLK+ | Reference Clock Differential pair |

| 14 | HSOp(0) | Transmitter Lane 0, Differential pair |

REFCLK- | |

| 15 | HSOn(0) | GND | Ground | |

| 16 | GND | Ground | HSIp(0) | Differential pair |

| 17 | PRSNT#2 | Hotplug detect | HSIn(0) | |

| 18 | GND | Ground | GND | Ground |

PCI-Express 4x Connector Pin-Out

| Pin |

Side B Connector |

Side A Connector |

||

| # | Name | Description | Name | Description |

| 1 | +12v | +12 volt power | PRSNT#1 | Hot plug presence detect |

| 2 | +12v | +12 volt power | +12v | +12 volt power |

| 3 | +12v | +12 volt power | +12v | +12 volt power |

| 4 | GND | Ground | GND | Ground |

| 5 | SMCLK | SMBus clock | JTAG2 | TCK |

| 6 | SMDAT | SMBus data | JTAG3 | TDI |

| 7 | GND | Ground | JTAG4 | TDO |

| 8 | +3.3v | +3.3 volt power | JTAG5 | TMS |

| 9 | JTAG1 | +TRST# | +3.3v | +3.3 volt power |

| 10 | 3.3Vaux | 3.3v volt power | +3.3v | +3.3 volt power |

| 11 | WAKE# | Link Reactivation | PWRGD | Power Good |

Mechanical Key |

||||

| 12 | RSVD | Reserved | GND | Ground |

| 13 | GND | Ground | REFCLK+ | Reference Clock Differential pair |

| 14 | HSOp(0) | Transmitter Lane 0, Differential pair |

REFCLK- | |

| 15 | HSOn(0) | GND | Ground | |

| 16 | GND | Ground | Receiver Lane 0, Differential pair |

|

| 17 | PRSNT#2 | Hotplug detect | HSIn(0) | |

| 18 | GND | Ground | GND | Ground |

| 19 | HSOp(1) | Transmitter Lane 1, Differential pair |

RSVD | Reserved |

| 20 | HSOn(1) | GND | Ground | |

| 21 | GND | Ground | HSIp(1) | Receiver Lane 1, |

| 22 | GND | Ground | HSIn(1) | |

| 23 | HSOp(2) | Transmitter Lane 2, Differential pair |

GND | Ground |

| 24 | HSOn(2) | GND | Ground | |

| 25 | GND | Ground | HSIp(2) | Receiver Lane 2, Differential pair |

| 26 | GND | Ground | HSIn(2) | |

| 27 | HSOp(3) | Transmitter Lane 3, Differential pair |

GND | Ground |

| 28 | HSOn(3) | GND | Ground | |

| 29 | GND | Ground | HSIp(3) | Receiver Lane 3, Differential pair |

| 30 | RSVD | Reserved | HSIn(3) | |

| 31 | PRSNT#2 | Hot plug detect | GND | Ground |

| 32 | GND | Ground | Reserved | |

PCI-Express 8x Connector Pin-Out

| Pin |

Side B Connector |

Side A Connector |

||

| # | Name | Description | Name | Description |

| 1 | +12v | +12 volt power | PRSNT#1 | Hot plug presence detect |

| 2 | +12v | +12 volt power | +12v | +12 volt power |

| 3 | +12v | +12 volt power | +12v | +12 volt power |

| 4 | GND | Ground | GND | Ground |

| 5 | SMCLK | SMBus clock | JTAG2 | TCK |

| 6 | SMDAT | SMBus data | JTAG3 | TDI |

| 7 | GND | Ground | JTAG4 | TDO |

| 8 | +3.3v | +3.3 volt power | JTAG5 | TMS |

| 9 | JTAG1 | +TRST# | +3.3v | +3.3 volt power |

| 10 | 3.3Vaux | 3.3v volt power | +3.3v | +3.3 volt power |

| 11 | WAKE# | Link Reactivation | PWRGD | Power Good |

|

Mechanical Keycard |

||||

| 12 | RSVD | Reserved | GND | Ground |

| 13 | GND | Ground | REFCLK+ | Reference Clock Differential pair |

| 14 | HSOp(0) | Transmitter Lane 0, Differential pair |

REFCLK- | |

| 15 | HSOn(0) | GND | Ground | |

| 16 | GND | Ground | HSIp(0) | Receiver Lane 0, Differential pair |

| 17 | PRSNT#2 | Hotplug detect | HSIn(0) | |

| 18 | GND | Ground | GND | Ground |

| 19 | HSOp(1) | Transmitter Lane 1, Differential pair |

RSVD | Reserved |

| 20 | HSOn(1) | GND | Ground | |

| 21 | GND | Ground | HSIp(1) | Receiver Lane 1, Differential pair |

| 22 | GND | Ground | HSIn(1) | |

| 23 | HSOp(2) | Transmitter Lane 2, Differential pair |

GND | Ground |

| 24 | HSOn(2) | GND | Ground | |

| 25 | GND | Ground | HSIp(2) | Receiver Lane 2, Differential pair |

| 26 | GND | Ground | HSIn(2) | |

| 27 | HSOp(3) | Transmitter Lane 3, Differential pair |

GND | Ground |

| 28 | HSOn(3) | GND | Ground | |

| 29 | GND | Ground | HSIp(3) | Receiver Lane 3, Differential pair |

| 30 | RSVD | Reserved | HSIn(3) | |

| 31 | PRSNT#2 | Hot plug detect | GND | Ground |

| 32 | GND | Ground | RSVD | Reserved |

| 33 | HSOp(4) | Transmitter Lane 4, Differential pair |

RSVD | Reserved |

| 34 | HSOn(4) | GND | Ground | |

| 35 | GND | Ground | HSIp(4) | Receiver Lane 4, Differential pair |

| 36 | GND | Ground | HSIn(4) | |

| 37 | HSOp(5) | Transmitter Lane 5, Differential pair |

GND | Ground |

| 38 | HSOn(5) | GND | Ground | |

| 39 | GND | Ground | HSIp(5) | Receiver Lane 5, Differential pair |

| 40 | GND | Ground | HSIn(5) | |

| 41 | HSOp(6) | Transmitter Lane 6, Differential pair |

GND | Ground |

| 42 | HSOn(6) | GND | Ground | |

| 43 | GND | Ground | HSIp(6) | Receiver Lane 6, Differential pair |

| 44 | GND | Ground | HSIn(6) | |

| 45 | HSOp(7) | Transmitter Lane 7, Differential pair |

GND | Ground |

| 46 | HSOn(7) | GND | Ground | |

| 47 | GND | Ground | HSIp(7) | Receiver Lane 7, Differential pair |

| 48 | PRSNT#2 | Hot plug detect | HSIn(7) | |

| 49 | GND | Ground | GND | Ground |

PCI-Express 16x Connector Pin-Out

| Pin |

Side B Connector |

Side A Connector |

||

| # | Name | Description | Name | Description |

| 1 | +12v | +12 volt power | PRSNT#1 | Hot plug presence detect |

| 2 | +12v | +12 volt power | +12v | +12 volt power |

| 3 | +12v | +12 volt power | +12v | +12 volt power |

| 4 | GND | Ground | GND | Ground |

| 5 | SMCLK | SMBus clock | JTAG2 | TCK |

| 6 | SMDAT | SMBus data | JTAG3 | TDI |

| 7 | GND | Ground | JTAG4 | TDO |

| 8 | +3.3v | +3.3 volt power | JTAG5 | TMS |

| 9 | JTAG1 | +TRST# | +3.3v | +3.3 volt power |

| 10 | 3.3Vaux | 3.3v volt power | +3.3v | +3.3 volt power |

| 11 | WAKE# | Link Reactivation | PWRGD | Power Good |

|

Mechanical Key |

||||

| 12 | RSVD | Reserved | GND | Ground |

| 13 | GND | Ground | REFCLK+ | Reference Clock Differential pair |

| 14 | HSOp(0) | Transmitter Lane 0, Differential pair |

REFCLK- | |

| 15 | HSOn(0) | GND | Ground | |

| 16 | GND | Ground | HSIp(0) | Receiver Lane 0, Differential pair |

| 17 | PRSNT#2 | Hotplug detect | HSIn(0) | |

| 18 | GND | Ground | GND | Ground |

| 19 | HSOp(1) | Transmitter Lane 1, Differential pair |

RSVD | Reserved |

| 20 | HSOn(1) | GND | Ground | |

| 21 | GND | Ground | HSIp(1) | Receiver Lane 1, Differential pair |

| 22 | GND | Ground | HSIn(1) | |

| 23 | HSOp(2) | Transmitter Lane 2, Differential pair |

GND | Ground |

| 24 | HSOn(2) | GND | Ground | |

| 25 | GND | Ground | HSIp(2) | Receiver Lane 2, Differential pair |

| 26 | GND | Ground | HSIn(2) | |

| 27 | HSOp(3) | Transmitter Lane 3, Differential pair |

GND | Ground |

| 28 | HSOn(3) | GND | Ground | |

| 29 | GND | Ground | HSIp(3) | Receiver Lane 3, Differential pair |

| 30 | RSVD | Reserved | HSIn(3) | |

| 31 | PRSNT#2 | Hot plug detect | GND | Ground |

| 32 | GND | Ground | RSVD | Reserved |

| 33 | HSOp(4) | Transmitter Lane 4, Differential pair |

RSVD | Reserved |

| 34 | HSOn(4) | GND | Ground | |

| 35 | GND | Ground | HSIp(4) | Receiver Lane 4, Differential pair |

| 36 | GND | Ground | HSIn(4) | |

| 37 | HSOp(5) | Transmitter Lane 5, Differential pair |

GND | Ground |

| 38 | HSOn(5) | GND | Ground | |

| 39 | GND | Ground | HSIp(5) | Receiver Lane 5, Differential pair |

| 40 | GND | Ground | HSIn(5) | |

| 41 | HSOp(6) | Transmitter Lane 6, Differential pair |

GND | Ground |

| 42 | HSOn(6) | GND | Ground | |

| 43 | GND | Ground | HSIp(6) | Receiver Lane 6, Differential pair |

| 44 | GND | Ground | HSIn(6) | |

| 45 | HSOp(7) | Transmitter Lane 7, Differential pair |

GND | Ground |

| 46 | HSOn(7) | GND | Ground | |

| 47 | GND | Ground | HSIp(7) | Receiver Lane 7, Differential pair |

| 48 | PRSNT#2 | Hot plug detect | HSIn(7) | |

| 49 | GND | Ground | GND | Ground |

| 50 | HSOp(8) | Transmitter Lane 8, Differential pair |

RSVD | Reserved |

| 51 | HSOn(8) | GND | Ground | |

| 52 | GND | Ground | HSIp(8) | Receiver Lane 8, Differential pair |

| 53 | GND | Ground | HSIn(8) | |

| 54 | HSOp(9) | Transmitter Lane 9, Differential pair |

GND | Ground |

| 55 | HSOn(9) | GND | Ground | |

| 56 | GND | Ground | HSIp(9) | Receiver Lane 9, Differential pair |

| 57 | GND | Ground | HSIn(9) | |

| 58 | HSOp(10) | Transmitter Lane 10, Differential pair |

GND | Ground |

| 59 | HSOn(10) | GND | Ground | |

| 60 | GND | Ground | HSIp(10) | Receiver Lane 10, Differential pair |

| 61 | GND | Ground | HSIn(10) | |

| 62 | HSOp(11) | Transmitter Lane 11, Differential pair |

GND | Ground |

| 63 | HSOn(11) | GND | Ground | |

| 64 | GND | Ground | HSIp(11) | Receiver Lane 11, Differential pair |

| 65 | GND | Ground | HSIn(11) | |

| 66 | HSOp(12) | Transmitter Lane 12, Differential pair |

GND | Ground |

| 67 | HSOn(12) | GND | Ground | |

| 68 | GND | Ground | HSIp(12) | Receiver Lane 12, Differential pair |

| 69 | GND | Ground | HSIn(12) | |

| 70 | HSOp(13) | Transmitter Lane 13, Differential pair |

GND | Ground |

| 71 | HSOn(13) | GND | Ground | |

| 72 | GND | Ground | HSIp(13) | Receiver Lane 13, Differential pair |

| 73 | GND | Ground | HSIn(13) | |

| 74 | HSOp(14) | Transmitter Lane 14, Differential pair |

GND | Ground |

| 75 | HSOn(14) | GND | Ground | |

| 76 | GND | Ground | HSIp(14) | Receiver Lane 14, Differential pair |

| 77 | GND | Ground | HSIn(14) | |

| 78 | HSOp(15) | Transmitter Lane 15, Differential pair |

GND | Ground |

| 79 | HSOn(15) | GND | Ground | |

| 80 | GND | Ground | HSIp(15) | Receiver Lane 15, Differential pair |

| 81 | PRSNT#2 | Hot plug present detect | HSIn(15) | |

| 82 | RSVD#2 | Hot Plug Detect | GND | Ground |

PRSNT#1 is connected to GND on motherboard.

Add on card needs to have PRSNT#1 connected to one of PRSNT#2 depending what type of connector is in use.

PCI-express standards

PCI Express 1.0a

In 2003, PCI-SIG introduced PCIe 1.0a, with a per-lane data rate of 250 MB/s and a transfer rate of 2.5 gigatransfers per second (GT/s). Transfer rate is expressed in transfers per second instead of bits per second because the number of transfers includes the overhead bits, which do not provide additional throughput; PCIe 1.x uses an 8b/10b encoding scheme, resulting in a 20% (= 2/10) overhead on the raw channel bandwidth.

PCI Express 2.0

PCI-SIG announced the availability of the PCI Express Base 2.0 specification on 15 January 2007. The PCIe 2.0 standard doubles the transfer rate compared with PCIe 1.0 to 5 GT/s and the per-lane throughput rises from 250 MB/s to 500 MB/s. Consequently, a 32-lane PCIe connector (×32) can support an aggregate throughput of up to 16 GB/s. PCIe 2.0 motherboard slots are fully backward compatible with PCIe v1.x cards. PCIe 2.0 cards are also generally backward compatible with PCIe 1.x motherboards, using the available bandwidth of PCI Express 1.1. Overall, graphic cards or motherboards designed for v2.0 will work with the other being v1.1 or v1.0a. Like 1.x, PCIe 2.0 uses an 8b/10b encoding scheme, therefore delivering, per-lane, an effective 4 Gbit/s max transfer rate from its 5 GT/s raw data rate.

PCI Express 2.1

PCI Express 2.1 (dated March 4, 2009) supports a large proportion of the management, support, and troubleshooting systems planned for full implementation in PCI Express 3.0. However, the speed is the same as PCI Express 2.0. The increase in power from the slot breaks backward compatibility between PCI Express 2.1 cards and some older motherboards with 1.0/1.0a, but most motherboards with PCI Express 1.1 connectors are provided with a BIOS update by their manufacturers through utilities to support backward compatibility of cards with PCIe 2.1.

PCI Express 3.0

PCI Express 3.0 specification was made available in November 2010. New features for the PCI Express 3.0 specification include a number of optimizations for enhanced signaling and data integrity, including transmitter and receiver equalization, PLL improvements, clock data recovery, and channel enhancements for currently supported topologies. PCI Express 3.0 upgrades the encoding scheme to 128b/130b from the previous 8b/10b encoding, reducing the bandwidth overhead from 20% of PCI Express 2.0 to approximately 1.54% (= 2/130). This is achieved by XORing a known binary polynomial as a scrambler to the data stream in a feedback topology. PCI Express 3.0’s 8 GT/s bit rate effectively delivers 985 MB/s per lane, nearly doubling the lane bandwidth relative to PCI Express 2.0.

PCI Express 4.0

PCI Express 4.0 was officially announced on 2017, providing a 16 GT/s bit rate that doubles the bandwidth provided by PCI Express 3.0, while maintaining backward and forward compatibility in both software support and used mechanical interface. PCI Express 4.0 specs will also bring OCuLink-2, an alternative to Thunderbolt connector. OCuLink version 2 will have up to 16 GT/s (8 GB/s total for ×4 lanes), while the maximum bandwidth of a Thunderbolt 3 connector is 5 GB/s. Additionally, active and idle power optimizations are to be investigated.

pinouts.ru

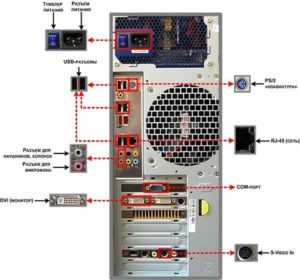

PCI распиновка — инструкция по распиновки всех разъемов ПК

PCI распиновка всех компьютерных разъемов

PCI распиновка — на этой странице предлагается обзор распиновки (распайки) компьютерных устройств периферии и ссылки. Попытка собрать то, что всегда нужно под рукой. Возможно это кому-то понадобится.

Внимание!!! Некоторые устройства могут иметь стандартные разъёмы и не стандартное подключение. Будьте бдительны!!!

- Разъемы данных (Южный мост):

- Кабель для подключения дисководов(Floppi).

Существуют как минимум два разных документа с разными данными:

Русскоязычный вариант:

Жилы с 10 по 16 после первого разъёма перекручены — необходимо для идентификации дисковода. Нечетные контакты — корпус.

- IDE(Integrated Drive Electronics )(По правильному называется — ATA/ATAPI — Advanced Technology Attachment Packet Interface, используется для подключения хардов и приводов).

По такой схеме можно подключить индикатор активности.

- SATA и eSATA (Одно и то-же, разница только в форме разъёма, это разъём данных, для подключения хардов и приводов).

DVD slim sata (распиновка стандарта мини сата).

- Распиновка USB-разъемов 1.0-2.0 (Universal Serial Bus).

USB 2.0 серии A, B и Mini

USB 2.0 Микро USB

Распиновка разъёма материнской платы для передней панели USB 2.0

- Распиновка USB-разъемов 3.0 (Universal Serial Bus).

USB 3.0 серии A, B, Micro-B и Powered-B. Серия Powered-B отличается от серии B, тем, что у него есть в наличии 2 дополнительных контакта, которые служат для передачи дополнительного питания, таким образом, устройство может получить до 1000 мА тока. Это снимает надобность в дополнительном источнике питания для маломощных устройств.

Распиновка разъёма материнской платы для передней панели USB 3.0

- Распиновка AT клавиатуры.

- Распиновка COM, LPT, GAME, RJ45, PS/2 порта и схема заглушки (COM, LPT).

Схема заглушки для тестирования COM-порта.

Схема заглушки для тестирования LPT-порта.

Схема заглушки

0 модемный кабель.

- Раскладка IEE 1394 на материнской плате

- Распиновка разьёма IEE 1394

Разъемы данных (Северный мост):

- Интерфейс AGP

- PCI Express: x1, x4, x8, x16

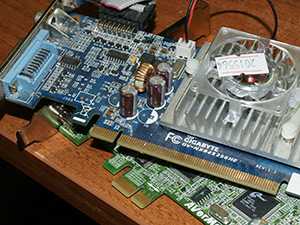

Чтобы видеокарта заработала в режиме x8 PCI Express, мы заклеили часть контактов скотчем.

Та же самая видеокарта, но заклеено больше контактов. Она работает в режиме x4 PCI Express.

Если заклеить лишние контакты, то видеокарта PCI Express станет работать в режиме всего x1 PCI Express. Пропускная способность составляет 256 Мбайт/с в обоих направлениях.

Разъемы данных (Общее):

- Контакты VGA, DVI, YC, SCART, AUDIO, RCA, S-VIDEO, HDMI, TV-ANTENNA.

- Обжим сетевого кабеля с разъёмом RJ45 (PC<>HUB, PC<>PC, HUB<>HUB).

- Распайка разъёмов GSM устройств (некоторых моделей сотовых телефонов).

- AUTO, MOTO

- Приложение (при работе с любыми данными, нужно уметь эти данные расшифровывать!).

В завершении получился, книжный вариант. Справочник, его версия в формате DOCX — оптимизирована печать (ставим 2-х стороннюю печать) и получаем брошюру. Которой можно: отбиваться при нашествии Зомби, Мух и Тараканов или растопить камин. Так же можно: просто разглядывать цветные картинки! Вариантов применения достаточно много…

А.Дансет — СПРАВОЧНИК ОБОЗНАЧЕНИЯ, РАЗЪЁМЫ И ИХ СОЕДИНЕНИЕ. 2014 ver:1.0 (В Печатном виде).

usilitelstabo.ru

| Pin | Side B Connector | Side A Connector | ||

| # | Name | Description | Name | Description |

| 1 | +12v | +12 volt power | PRSNT#1 | Hot plug presence detect |

| 2 | +12v | +12 volt power | +12v | +12 volt power |

| 3 | +12v | +12 volt power | +12v | +12 volt power |

| 4 | GND | Ground | GND | Ground |

| 5 | SMCLK | SMBus clock | JTAG2 | TCK |

| 6 | SMDAT | SMBus data | JTAG3 | TDI |

| 7 | GND | Ground | JTAG4 | TDO |

| 8 | +3.3v | +3.3 volt power | JTAG5 | TMS |

| 9 | JTAG1 | +TRST# | +3.3v | +3.3 volt power |

| 10 | 3.3Vaux | 3.3v volt power | +3.3v | +3.3 volt power |

| 11 | WAKE# | Link Reactivation | PWRGD | Power Good |

| Mechanical Key | ||||

| 12 | RSVD | Reserved | GND | Ground |

| 13 | GND | Ground | REFCLK+ | Reference Clock Differential pair |

| 14 | HSOp(0) | Transmitter Lane 0, Differential pair | REFCLK- | |

| 15 | HSOn(0) | GND | Ground | |

| 16 | GND | Ground | HSIp(0) | Receiver Lane 0, Differential pair |

| 17 | PRSNT#2 | Hotplug detect | HSIn(0) | |

| 18 | GND | Ground | GND | Ground |

| 19 | HSOp(1) | Transmitter Lane 1, Differential pair | RSVD | Reserved |

| 20 | HSOn(1) | GND | Ground | |

| 21 | GND | Ground | HSIp(1) | Receiver Lane 1, Differential pair |

| 22 | GND | Ground | HSIn(1) | |

| 23 | HSOp(2) | Transmitter Lane 2, Differential pair | GND | Ground |

| 24 | HSOn(2) | GND | Ground | |

| 25 | GND | Ground | HSIp(2) | Receiver Lane 2, Differential pair |

| 26 | GND | Ground | HSIn(2) | |

| 27 | HSOp(3) | Transmitter Lane 3, Differential pair | GND | Ground |

| 28 | HSOn(3) | GND | Ground | |

| 29 | GND | Ground | HSIp(3) | Receiver Lane 3, Differential pair |

| 30 | RSVD | Reserved | HSIn(3) | |

| 31 | PRSNT#2 | Hot plug detect | GND | Ground |

| 32 | GND | Ground | RSVD | Reserved |

| 33 | HSOp(4) | Transmitter Lane 4, Differential pair | RSVD | Reserved |

| 34 | HSOn(4) | GND | Ground | |

| 35 | GND | Ground | HSIp(4) | Receiver Lane 4, Differential pair |

| 36 | GND | Ground | HSIn(4) | |

| 37 | HSOp(5) | Transmitter Lane 5, Differential pair | GND | Ground |

| 38 | HSOn(5) | GND | Ground | |

| 39 | GND | Ground | HSIp(5) | Receiver Lane 5, Differential pair |

| 40 | GND | Ground | HSIn(5) | |

| 41 | HSOp(6) | Transmitter Lane 6, Differential pair | GND | Ground |

| 42 | HSOn(6) | GND | Ground | |

| 43 | GND | Ground | HSIp(6) | Receiver Lane 6, Differential pair |

| 44 | GND | Ground | HSIn(6) | |

| 45 | HSOp(7) | Transmitter Lane 7, Differential pair | GND | Ground |

| 46 | HSOn(7) | GND | Ground | |

| 47 | GND | Ground | HSIp(7) | Receiver Lane 7, Differential pair |

| 48 | PRSNT#2 | Hot plug detect | HSIn(7) | |

| 49 | GND | Ground | GND | Ground |

| 50 | HSOp(8) | Transmitter Lane 8, Differential pair | RSVD | Reserved |

| 51 | HSOn(8) | GND | Ground | |

| 52 | GND | Ground | HSIp(8) | Receiver Lane 8, Differential pair |

| 53 | GND | Ground | HSIn(8) | |

| 54 | HSOp(9) | Transmitter Lane 9, Differential pair | GND | Ground |

| 55 | HSOn(9) | GND | Ground | |

| 56 | GND | Ground | HSIp(9) | Receiver Lane 9, Differential pair |

| 57 | GND | Ground | HSIn(9) | |

| 58 | HSOp(10) | Transmitter Lane 10, Differential pair | GND | Ground |

| 59 | HSOn(10) | GND | Ground | |

| 60 | GND | Ground | HSIp(10) | Receiver Lane 10, Differential pair |

| 61 | GND | Ground | HSIn(10) | |

| 62 | HSOp(11) | Transmitter Lane 11, Differential pair | GND | Ground |

| 63 | HSOn(11) | GND | Ground | |

| 64 | GND | Ground | HSIp(11) | Receiver Lane 11, Differential pair |

| 65 | GND | Ground | HSIn(11) | |

| 66 | HSOp(12) | Transmitter Lane 12, Differential pair | GND | Ground |

| 67 | HSOn(12) | GND | Ground | |

| 68 | GND | Ground | HSIp(12) | Receiver Lane 12, Differential pair |

| 69 | GND | Ground | HSIn(12) | |

| 70 | HSOp(13) | Transmitter Lane 13, Differential pair | GND | Ground |

| 71 | HSOn(13) | GND | Ground | |

| 72 | GND | Ground | HSIp(13) | Receiver Lane 13, Differential pair |

| 73 | GND | Ground | HSIn(13) | |

| 74 | HSOp(14) | Transmitter Lane 14, Differential pair | GND | Ground |

| 75 | HSOn(14) | GND | Ground | |

| 76 | GND | Ground | HSIp(14) | Receiver Lane 14, Differential pair |

| 77 | GND | Ground | HSIn(14) | |

| 78 | HSOp(15) | Transmitter Lane 15, Differential pair | GND | Ground |

| 79 | HSOn(15) | GND | Ground | |

| 80 | GND | Ground | HSIp(15) | Receiver Lane 15, Differential pair |

| 81 | PRSNT#2 | Hot plug present detect | HSIn(15) | |

| 82 | RSVD#2 | Hot Plug Detect | GND | Ground |

itcblog.ru

Подробно о Распиновка pci express x16

В наше время слова «Майнинг», «Блокчейн», «Биткоины» раздаются буквально отовсюду: от пассажиров трамвая до серьёзных бизнесменов и депутатов Госдумы. Разобраться во всех тонкостях и подводных камнях этих и смежных понятий сложно, однако в базе данных на нашем сайте Вы быстро найдёте исчерпывающую информацию, касающуюся всех аспектов.

Ищем дополнительную информацию в базах данных:

Распиновка pci express x16

Базы онлайн-проектов:

Данные с выставок и семинаров:

Данные из реестров:

Дождитесь окончания поиска во всех базах.

По завершению появится ссылка для доступа к найденным материалам.

Вкратце же все необходимые знания будут изложены в этой статье.

Итак, начать стоит с блокчейна. Суть его в том, что компьютеры объединяются в единую сеть через совокупность блоков, содержащую автоматически зашифрованную информацию, попавшую туда. Вместе эти блоки образуют базу данных. Допустим, Вы хотите продать дом. Оформив документы, необходимо идти к нотариусу, затем в присутствии его, заверив передачу своей подписью, Вам отдадут деньги. Это долго, да и к тому же нужно платить пошлину.

Благодаря технологии блокчейна достаточно:

- Договориться.

- Узнать счёт получателя.

- Перевести деньги на счёт получателя.

…и не только деньги. Можно оформить электронную подпись и отправлять документы, любую другую информацию, в том числе и конфиденциальную. Опять же, не нужны нотариусы и другие чиновники: достаточно идентифицироваться Вам и получателю (будь то частное лицо или госучреждение) в своём компьютере.

Транзакция проходит по защищённому каналу связи, никто не видит (в том числе банки и государство), кто, что и кому перевёл.

Возможность взломать исключена из-за огромного количества блоков, описанных выше. Для хакера нужно подобрать шифр для каждого блока, что физически нереально.

Другие возможности использования блокчейна:

- Страхование;

- Логистика;

- Оплата штрафов

- Регистрация браков и многое другое.

С блокчейном тесно связано понятие криптовалюта. Криптовалюта — это новое поколение децентрализованной цифровой валюты, созданной и работающей только в сети интернет. Никто не контролирует ее, эмиссия валюты происходит посредством работы миллионов компьютеров по всему миру, используя программу для вычисления математических алгоритмов.

Вкратце это выглядит так:

1. Вы намереваетесь перевести кому-то деньги.

2. Генерируется математический код, проходящий через уже известные Вам блоки.

3. Множество компьютеров (часто представляющих собой совокупность их, с мощными процессорами и как следствие большей пропускной способностью) обрабатывают цифровую информацию, передавая их на следующие блоки, получая за это вознаграждение (некоторые транзакции можно совершать бесплатно)

4. Математический код доходит до электронного кошелька получателя, на его балансе появляются деньги.

Опять же, как это в случае с блокчейном, переводы криптовалют никем не контролируются.

Хотя база данных открыта, со всеми адресами переводящих и получающих деньги, но владельца того или иного адреса, с которого осуществляется перевод, никто не знает, если только хозяин сам не захочет рассказать.

Работающих по подобному принципу валют много. Самой знаменитой является, конечно, биткоин. Также популярны эфириум, ритл, лайткоины, нумитсы, неймкоины и многие другие. Разница у них в разном типе шифрования, обработки и некоторых других параметрах.

Зарабатывают на технологии передачи денег майнеры.

Это люди, создавшие упомянутую выше совокупность компьютерных видеокарт, которая генерирует новые блоки, передающие цифровую информацию — биткоины (или ритлы, или любую другую криптовалюту). За это они получают вознаграждение в виде той же самой криптовалюты.

Существует конкуренция между майнерами, т.к. технология с каждой транзакции запрограммировано усложняется. Сначала можно было майнить с одного компьютера (2008 год), сейчас же такую валюту как биткоин физическим лицам уже просто невыгодно: нужно очень много видеокарт (их все вместе называют фермами), с огромными вычислительными мощностями. Для этого снимаются отдельные помещения, затраты электроэнергии для работы сравнимы с затратами промышленных предприятий.

Зато можно заработать на других, менее популярных, но развивающихся криптовалютах. Также различают соло майнинг и пул майнинг. Соло — это создание своей собственной фермы, прибыль забирается себе. Пул же объединяет других людей с такими же целями. Заработать можно гораздо больше, но придётся уже делиться со всеми.

Перспективами использования технологии блокчейна вообще и криптовалют в частности заинтересовались как и физические лица, так и целые государства.

В Японии криптовалюта узаконена. В России в следующем году собираются принять нормативно-правовые акты о легализации блокчейна, переводов криптовалюты и майнинга. Планируется перевод некоторых операций в рамки блокчейна. Имеет смысл изучить это подробнее, и, при желании, начать зарабатывать. Очевидно, что сейчас информационные технологии будут развиваться и входить в нашу жизнь всё больше и больше.

safe-crypto.me

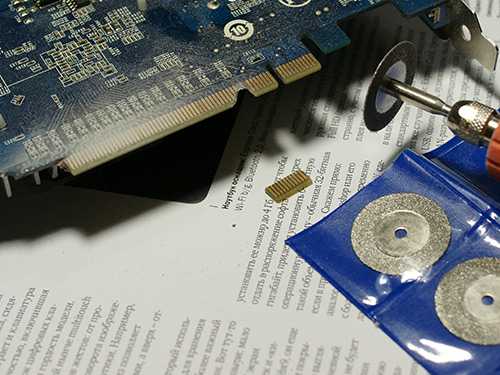

Отпиливаем часть разъёма PCI Express x16

Примеры неудачного превращения видеокарты с интерфейсом PCI Express x16 в видеокарту с интерфейсом PCI при помощи режущих инструментов нам уже известны. Хотя в названии этих интерфейсов и есть общие буквы, физически они имеют существенные отличия. Заставить видеокарту с интерфейсом PCI Express x16 работать в слоте PCI без специального переходника с чипом-мостом не только невозможно, но и не имеет смысла. Во всяком случае, потери пропускной способности шины составят несколько тысяч процентов :).Другое дело, если видеокарту с интерфейсом PCI Express x16 нужно установить в слот PCI Express x8, PCI Express x4 или PCI Express x1. Стандарт PCI Express изначально разрабатывался с учётом обеспечения обратной совместимости, но на практике помехой может стать механическая несовместимость. Производители материнских плат иногда побеждают и её, делая слоты PCI Express x4 с так называемым «открытым пазом», что позволяет устанавливать в них видеокарту с интерфейсом PCI Express x16. Единственное неудобство — снижение пропускной способности графической шины до PCI Express x4, но иногда оно не так критично, и совместимость важнее. Иногда слот PCI Express x4 на материнских платах имеет конструктивную форму PCI Express x16, это лишь позволяет лучше зафиксировать видеокарту.

Разъём PCI Express x16 устроен так, что следующие за 11-ым штырьком контакты (нумерация начинается с 0) отвечают исключительно за повышение пропускной способности интерфейса. Поэтому, если слот PCI Express x1 имеет открытый паз, то обычная видеокарта с интерфейсом PCI Express x16 тоже сможет в нём работать — в режиме PCI Express x1, разумеется.

Этим свойством воспользовались некие японские энтузиасты, наверняка посещавшие в детстве кружок «Шальные лобзики» :). Они взяли видеокарту GeForce 6600 LE с интерфейсом PCI Express x16, и отпилили «лишнюю» часть интерфейсного разъёма таким образом, что графическую плату удалось установить в материнскую плату Tyan Tiger i7520SD, которая имеет только два слота PCI Express x8 с закрытым пазом.

Видеокарта прекрасно работала после такой «ампутации», в планах японских любителей резьбы по текстолиту адаптировать для этой материнской платы пару видеокарт класса GeForce 7600, чтобы эксплуатировать их в режиме SLI.

Соглашусь, что с проблемой подобной адаптации сталкивается не каждый пользователь, ведь рассматриваемая материнская плата относится к классу серверных продуктов. Кроме того, такие манипуляции способны вывести из строя видеокарту или даже материнскую плату, если что-то будет сделано неправильно. На ампутацию при помощи инструментов уходит минут десять, но обратного пути уже нет. Безусловно, повторять этот трюк дома не следует :).

overclockers.ru

Распиновки слотов расширения на материнской плате распиновка и описание @ pinouts.ru

Распиновки слотов расширения на материнской плате распиновка и описание @ pinouts.ru- CardBus 32-bit bus defined by PCMCIA.

- CompactPCI bus PCI=Peripheral Component Interconnect. CompactPCI is a version of PCI adapted for industrial and/or embedded applications.

- FireWire (IEEE1394) bus interface Defined by IEEE 1394-1995 standard as a serial data transfer protocol and interconnection system. Also known as iLink (Sony) or Lynx. Often implemented in consumer electronics devices, digital video cameras, VCRs, some other multimedia hardware and computers.

- IndustrialPCI bus PCI=Peripheral Component Interconnect. IndustrialPCI is a version of PCI adapted for industrial and/or embedded applications.

- Mini PCI bus Mini PCI is an alternate PCI implementation designed for small form factor. It´s specification is a sub-set of PCI standard using 100 pin (Type I/II) or 124 pin (Type III) connector.

- PC/104 bus PC/104 is a compact version of the ISA bus. PC/104 is intended for specialized embedded computing environments where applications depend on reliable data acquisition despite an often extreme environment.

- PCI bus The PCI Bus is a high performance bus for interconnecting chips, expansion boards, and processor/memory subsystems.

- PCI Express 1x, 4x, 8x, 16x bus PCI Express (PCIe, PCI-e) is a high-speed serial computer expansion bus standard.

- PCI Express Mini Card (Mini PCIe) PCI Express Mini Card (also known as Mini PCI Express, Mini PCIe, and Mini PCI-E) is a replacement for the Mini PCI form factor based on PCI Express. It is developed by the PCI-SIG. The host device supports both PCI Express and USB 2.0 connectivity, and each card uses whichever the designer feels most appropriate to the task. Most laptop computers built after 2005 are based on PCI Express and can have several Mini Card slots.

- PCMCIA (PC Card) bus The PCMCIA (Personal Computer Memory Card International Association) 16 bit bus

- USB USB (Universal Serial Bus) designed to connect peripherals such as mice, keyboards, scanners, digital cameras, printers, hard disks, and networking components to PC. It has become the standard connection method for wide variety of devices.

- USB 3.0 connector USB 3.0 is the successor of USB 2.0. USB 3 reduces the time required for data transmission, reduces power consumption, and is backward compatible with USB 2.0

- USB Type C

- VME64x bus

- VMEbus VMEbus is a computer bus standard originally developed for the Motorola 68000 line of CPUs, but later widely used for many applications.

Распиновки для Apple

- ADB Apple Desktop Bus ADB is a low-speed serial bus used on Apple Macintosh computers manufactured in 1986-1999. It’s used to connect input devices (such as the mouse or keyboard) to the CPU

- Apple Communication Slot Available on Apple Macintosh 575, 630, 5200 5300 and Apple Performa 6200CD, 6300 series

- Apple Duo Dock Available on Apple Duo Dock & Duo Dock II dockingstations. For use with Apple PowerBook Duo computers.

Распиновки для Asus

pinouts.ru

Как установить PCI Express x16 видеокарту в слот PCI Express x8

Места для маневров по расширению возможностей стоечного 1U-сервера не так уж много. Разве что — установка дополнительного PCI Express адаптера с помощью угловой Riser-карты, известной под названием «гребёнка». Во времена Legacy PCI даже это скудное решение обладало универсальностью: все платы расширения по разъемам были идентичны.

Шина PCIe, в отличие от предшественницы, радует разнообразием. Видеокарты используют разъемы x16, другие контроллеры — x8. Разработчики платформы Supermicro X8SIL здраво рассудили, что для серверной платы, оснащенной бортовым видео, максимум масштабирования — внешний PCI Express адаптер с шириной шины x8.

Как в создавшихся условиях установить дополнительную видеокарту, ведь и на системной плате, и на Riser Card есть только слот PCI Express x8? На каком видеоадаптере остановиться, исходя из ограничений на типоразмер и жестких требований к терморежиму?

Очевидно, что использование так называемых «тихих» решений от ASUS соответствует поставленной задаче. Компактная безвентиляторная видеокарта EAH6250 вполне подходит под указанные требования. Ее радиатор высотой не более 15 миллиметров позволяет установить устройство в Riser Card, не конфликтуя с элементами конструктива шасси на платформе Supermicro X8SIL.

Решив вопрос комплектации, рассмотрим, как добиться совместимости PCI Express x16 видеокарты с разъемом расширения PCIe x8? Прежде всего, уточним для себя, что работоспособность шины PCI Express зависит от успешного прохождения таких процедур:

- детектирование установленного адаптера;

- определение ширины линка;

- согласование полосы пропускания.

Детектирование устройства

Для детектирования устройств в слотах PCI Express используется механизм, основанный на сигналах шины PRSNT#1 и PRSNT#2. Их мнемоника говорит сама за себя: Present — значит В наличии.

Рис 1. Hot-Plug: укороченные ламели, размещенные по краям разъема, при установке замыкаются последними,

а при извлечении размыкаются первыми

Необходимость обслуживания «горячего подключения», заложенного в PCIe-стандарт, требует их исполнения в виде укороченных ламелей и в некоторых случаях размещения только по краям разъема. Соблюдение этого условия при подключении устройств с различной шириной линка («link width») обеспечивается несколькими копиями сигнала PRSNT#2.

Рис 2. PCI Express x8 Riser карты Supermicro RR1U-E8 готовятся для установки адаптеров PCIe x16

Установка видеокарты PCI Express x16 в Riser Card x8 приводит к тому, что сигнал PRSNT#2, заведенный на контакт B81, остается неподключенным. Его заземление на системной плате обеспечит успешное детектирование устройства. Для этого закорачиваются контакты B48 и B49 на PCI Express Riser Card.

Рис 3. Гребёнка готова к использованию:

разъем доработан для установки плат PCIe x16,

запаяна перемычка между контактами B48 и B49.

Факторы совместимости

Видеокарта PCI Express x16, установленная в слот PCI Express x8, сохраняет работоспособность, благодаря процедуре PCIe Link Training, на которую возлагается определение ширины линка и согласование полосы пропускания.

Рис 4. Бесшумный PCI Express x16 видеоадаптер от ASUS, модель EAH6450 установлен в PCIe Riser x8;

за счет этого расширена функциональность платформы Supermicro X8SIL

Такая процедура создает предпосылки для возникновения весьма «коварных» дефектов: успешный старт и инициализация VGA-контроллера возможны даже при деградации параметров соединения. Нужно убедиться, что рассматриваемая конструкция работает в режиме x8.

Рис 5. Снимок с экрана: диагностика подключения с помощью специализированного теста демонстрирует

производительность платформы в режиме x8 с пропускной способностью в 2.5 GT/sec

Исходя из результатов тестирования в среде операционной системы можно сказать, что фактически подтверждена работоспособность PCI Express x16 устройства в разъеме меньшей размерности PCIe x8.

Вместо резюме

В большинстве ситуаций факторами, ограничивающими интегральное быстродействие видео адаптера, являются производительность GPU и особенности интерфейса видео памяти. Уменьшение ширины шины PCI Express в два раза, безусловно повлияет на параметры видео подсистемы, но двукратного снижения основных показателей по сравнению с вариантом x16 при прочих равных условиях, ожидать не следует, в силу того, что порт PCIe является только одним из фрагментов достаточно сложной цепи передачи и обработки информации. Максимальное влияние ширины PCIe-линка будет ощутимо разве что в синтетических бенчмарках, измеряющих скорость записи в видеопамять как выделенную метрику.

composter.com.ua